- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: LTDC problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LTDC problem

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-09 10:03 AM

Hello,

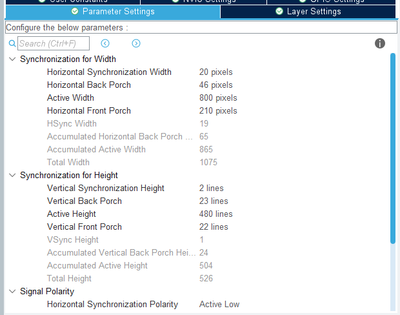

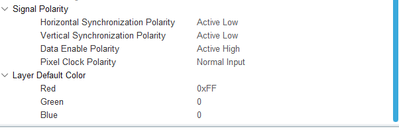

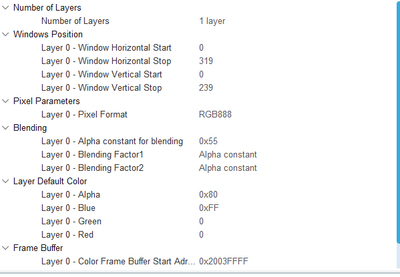

i have problem with custom board assembled with STM32F767BIT6. I'm trying to interfacing LCD-TFT DEM 800480K3 TMH-PW-N which is assembled by HX8264E, HX8664B drivers. I'm using RGB888 interface configured via STMCubeIDE filled by resolution 800x480 with 1 layer and small buffer 320x240 located in internal SRAM on address 0x2003FFFF(i have 8MB external SDRAM but i'm trying to use small buffer in SRAM for workaround first), inverted DE polarity, clock for LTDC is 32MHz. But LCD still doesn't work. So i connected oscilloscope and i see correct 32MHz pixel clock, i see correct HSYNC but VSYNC is always low and DE sometimes sent some chaotic pulses or rest arround 1,7V. I checked connection on HW and it looks fine.

(When i try full resolution 800x480 for layer i've got transfer data error and fifo underrun error. When i tried external SDRAM which is probably badly configured im not unable to reflash STM because STLink is not able to find my STM32, then i have to full erase chip via STM32CubeProgrammer.) So i decided start wit small window buffer in internal SRAM.

Do you have any idea, where can be the issue?

Solved! Go to Solution.

- Labels:

-

STM32F7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-10 09:13 AM

I tried to switch DE to active low and now everything is working fine. Now im going to experiment with 2 layers and external SDRAM.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-10 09:13 AM

I tried to switch DE to active low and now everything is working fine. Now im going to experiment with 2 layers and external SDRAM.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-11 03:25 AM

Hello @Petr3,

Glad to now that the issue is solved. And thank you for updating post and sharing the solution.

About the DE, it is mentioned in AN4861 that "Only the DE control signal must be inverted versus the DE polarity indicated in the display datasheet. The other control signals must be configured exactly like the display datasheet."

For example if you referring to the display datasheet, and you found that HSYNC and VSYNC must be active low and the DE signal must be active high. In this case, as the DE signal is inverted in the output, it must be set to active

low as well. The LCD_CLK signal must not be inverted.

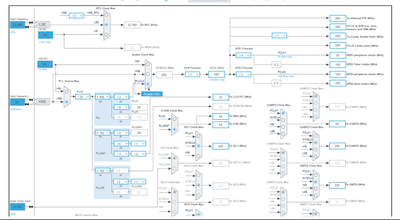

I recommend you to take a look to LCD-TFT display controller (LTDC) on STM32 MCUs, I think can help you to configure 2 Layers and external SDRAM.

I hope this help you.

Thank you for your contribution in STCommunity :).

Kaouthar

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Unstable logical state on every I/O pin in STM32 MCUs Products

- Overrun problem with USART2 in STM32H723 MCU in STM32 MCUs Embedded software

- Stm32H747I-DISCO Share Peripherals in STM32 MCUs Boards and hardware tools

- STM32WB55RCV6 BLE -- after hci_reset() no reply obtained from coprocessor running BLE stack in STM32 MCUs Wireless

- TouchGFX - Error during "Generate code" in STM32 MCUs TouchGFX and GUI