- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Is there a list of compatible I2C isolators for th...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Is there a list of compatible I2C isolators for the STM32F030 line?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-12 7:25 AM

Hello there,

We are using your STM32F030K6T6TR MCUs extensively in our Fotokite systems. They communicate via I2C. We have different MCUs on different, isolated grounds and are therefore currently using the Si8602AC-B-IS I2C isolator. This device does not correspond too well with the logic low voltages of the STM32F030K6T6TR. Are there any recommended (ST?) I2C isolators that are operating in the correct logic high and logic low levels?

Best

Alex

- Labels:

-

I2C

-

STM32F0 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-12 1:15 PM

STM32 is 5 volt tolerant on the I2C pins (and others from past reviews). What are the issues you are facing?

Suggesting that you have a 3k local pull-up on the i2c_sda line to +5v on the STM32 as shown on their page # 9 (Figure 3.3). BVDD = +5v. AVDD = whatever is suitable for your other side of the interface.

On i2c, the logic is open drain so there is a logic low but when "1" = pin is hi-z so the external pull-up sets the logic "high" value.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-13 7:05 AM

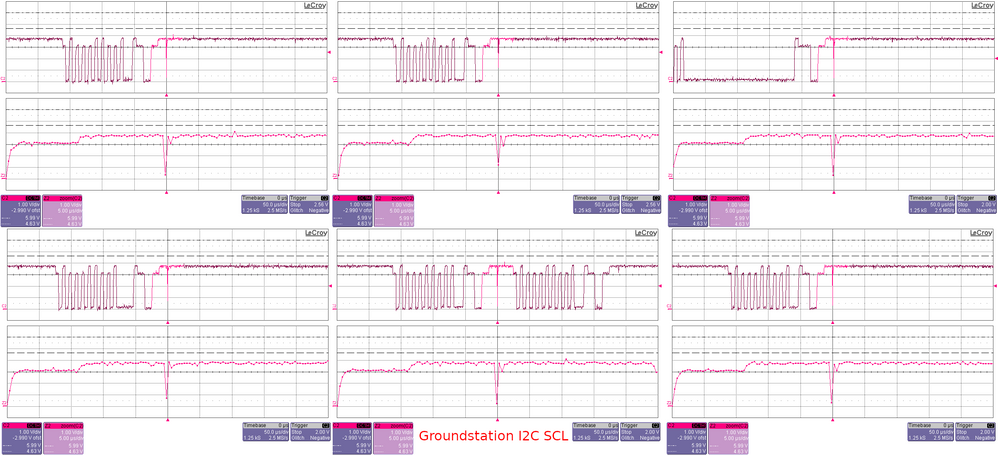

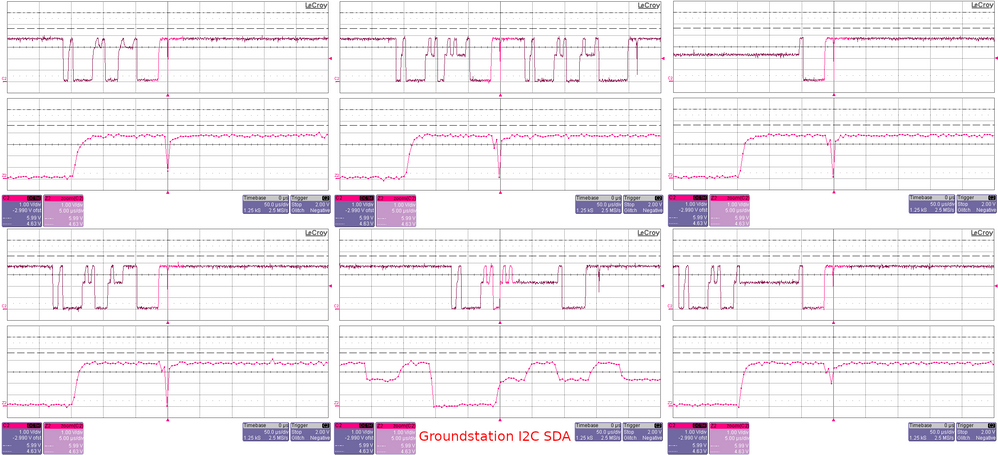

We are running the I2C on the 3.3V supplies. On A and B side is one or two MCUs connected. Pullups on SDA lines are 3.3kOhm. On the second look, it seems that the logic levels are indeed in the specified range. While sniffing the I2C comms I took notice of a 1us negative pulse after each message on the bus. This pulse can be seen on the SDA and SCL line. I believe this is what makes the communications unstable. See the attached plot of the SDA lines. I guess this isn't an issue of the STM MCU. Anyone has ever seen this?

Pics of the 6 separate measurements, including a zoom-in on the 1us pulse:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-13 7:45 AM

Hi. The spike does look to be strange.

1) Do you see this spike if the isolator is removed off the PCB?

2) Do you have the local despike caps as per the datasheet recommendation and close to the isolator?

3) We use Silabs isolators in high volume with zero issues. Also have used isolators from TI & NVE without issues. However, never used for I2C isolation.

4) From a quick review, you are using the 8 pin SOIC version of this I2C isolator? If yes, it appears that the TI I2C isolator p/n ISO1541 should be a drop in replacement. The TI version is recommending for a pull-up even on the SCL line. Perhaps you can perform a quick swap and try again.

http://www.ti.com/product/ISO1541

Very interested to hear about your results. Please update this thread as you continue to debug.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-15 4:19 AM

Thanks Mon2 for your answer.

1) It seems the glitch is not coming from the before mentioned STM32F0 or isolator, but from a STM32F405VGT6 (master device). I'm a bit confused, except from a simple T-filter nothing else is installed on the I2C lines and the glitch is clearly related to sending an I2C message. I must have a look at the code now, but as far as I'm concerned this shouldn't happen with a properly initialized I2C interface.

2) Despike caps are there.

4) I do have the ISO 1541 in-house for later evaluation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-09 11:32 PM

To close this topic, quick summary over found issues:

We are using clock stretching for I2C communications which gave us timing problems when the slave device was supposed to acknowledge a message. We therefore switched to a two channel bidirectional (Si8602 is one channel bidirectional, one unidirectional) isolator and the error rate has decreased to practically zero.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-09 11:34 PM

The seen spikes are artefacts of this failed clock stretching, where the I2C peripherie reinitializes.