- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Independent Dead-time for Advanced Timer

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Independent Dead-time for Advanced Timer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-20 4:50 PM

Hi All,

I'm using the advanced timer TIM1 on STM32303VC to drive a 2 phase shifted full bridges separated by a transformer (Dual Active Bridge topology). This required use of 4 PWMs. CH1 and CH1N drive the primary bridge. CH3 and CH3N drive the secondary bridge.

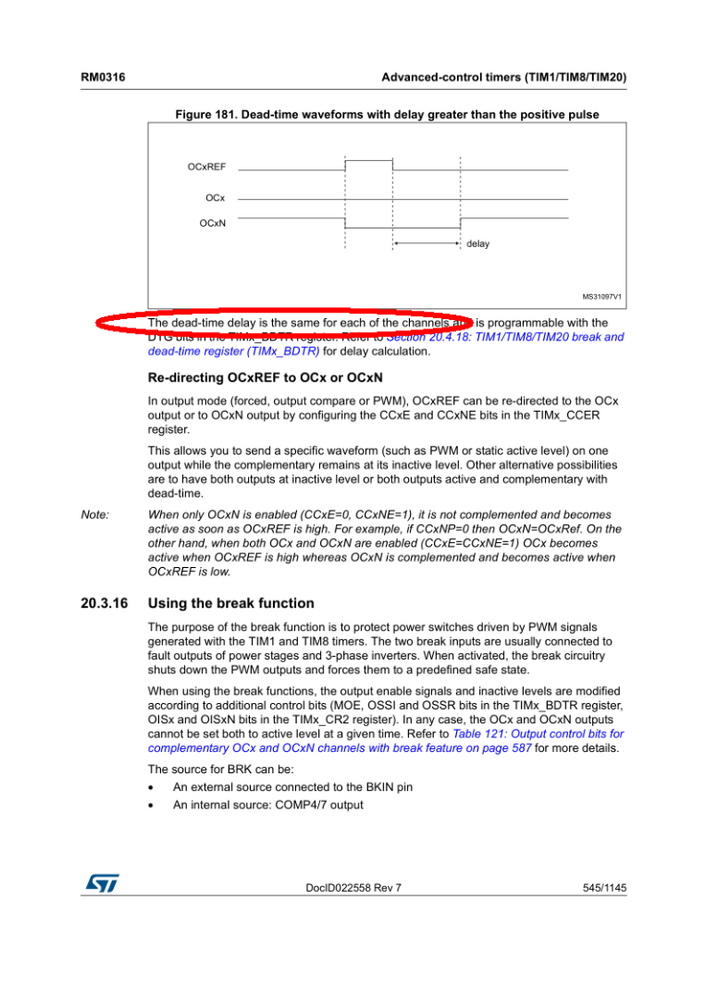

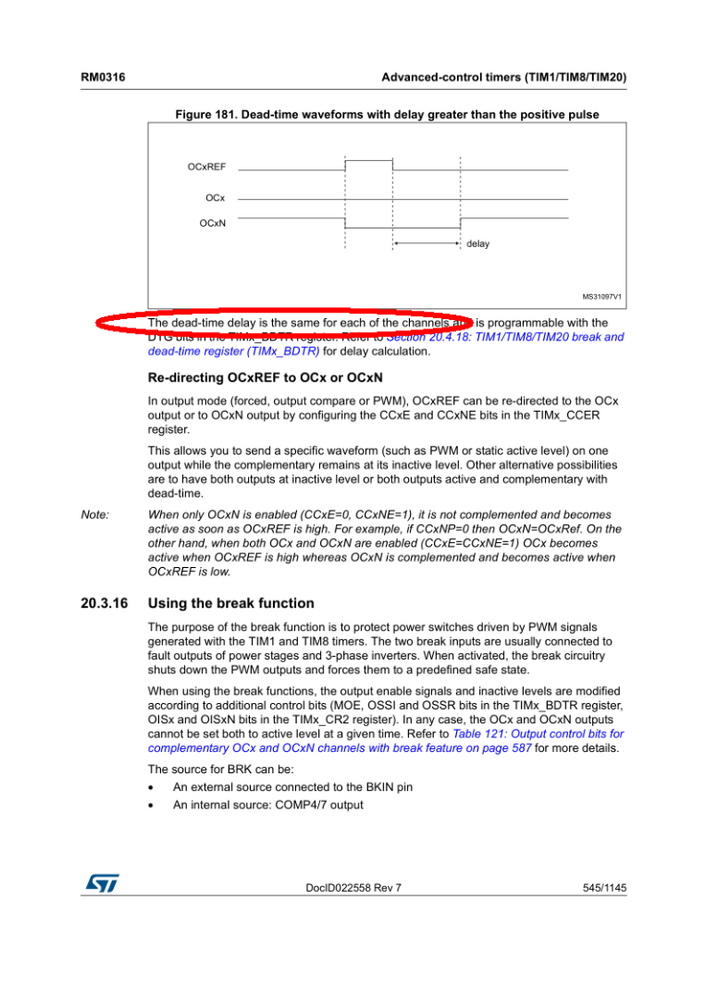

The question is I need to program independent dead times (for CH1-CH1N and CH3-CH3N). Is that possible? Because the LL APIs have only one dead time configuration value per Timer.

If it's not possible what is the workaround? This is a make or break situation for my converter.

Regards,

Vivek

#phase-shift #advanced-timers #timer-synchronizationSolved! Go to Solution.

- Labels:

-

TIM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-21 1:53 AM

The question is I need to program independent dead times (for CH1-CH1N and CH3-CH3N). Is that possible?

No.

If it's not possible what is the workaround?

Using two different timers?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-21 1:53 AM

The question is I need to program independent dead times (for CH1-CH1N and CH3-CH3N). Is that possible?

No.

If it's not possible what is the workaround?

Using two different timers?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-21 7:27 AM

Thanks JW.

Can I apply phase shift if I drive the bridges using two different timers? Also I need to apply this work around in my existing hardware. So that means I can configure Tim1_ch3-ch3n as input high impedance and short it with Tim8_ch1-ch1n. That should work right?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-24 6:04 PM

Vivek,

The STM32F334 has the HRTIM with an independent deadtime control for each channel.

Why your phase shift bridge need independent deadtime?

Ari.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-24 6:39 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-25 3:58 AM

Thanks for sharing your solution.

The reference manual mentions resynchronization delay but it never mentions what value will this resync. delay be.

Good question; I've never seen the inter-timer TRGO-TRGI delay properly specified - maybe in some of the appnotes?. TIMx_SMCR.MSM bit description vaguely hints about delaying the effect of TRGI ' to allow a perfect synchronization between the current timer and its slaves'; I've never tried that either.

JW

- confirmation for the LPTIM present in the STM32C011J6Px in STM32 MCUs Products

- PWM output on PA8 (TIM1_CH1) does not reach 0V — waveform distorted in STM32CubeIDE (MCUs)

- unexpected PWM is observed at output side. in STM32 MCUs Embedded software

- STM32CubeMX bug report in STM32CubeMX (MCUs)

- STM32G431 SPI Strange Data in STM32 MCUs Products