- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- In theory, you can use all 26 bit of the STM32U MD...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

In theory, you can use all 26 bit of the STM32U MDF in the CIC stage. In practice, I recommend to stay < 25 bit to avoid artifacts and saturation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-09-22 1:06 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-09-29 1:15 AM

Hello @Andreas Köpke,

Can you provide more details about your observation, please?

In which condition you saw artefacts and saturation?

Thank you for your feedback,

Gwénolé

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-09-29 1:52 AM

Another point,

The MDF FIFO is set to 24 bits like CIC output can be extended to 26 bits. Then, to fit with FIFO it's mandatory to use the SCALE block.

In case you enabled the INT block after CIC + SCALE blocks, then there is no possibility to adjust the output size from 26 bits to 24 bits.

Best regards,

Gwénolé

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-09-29 6:54 AM

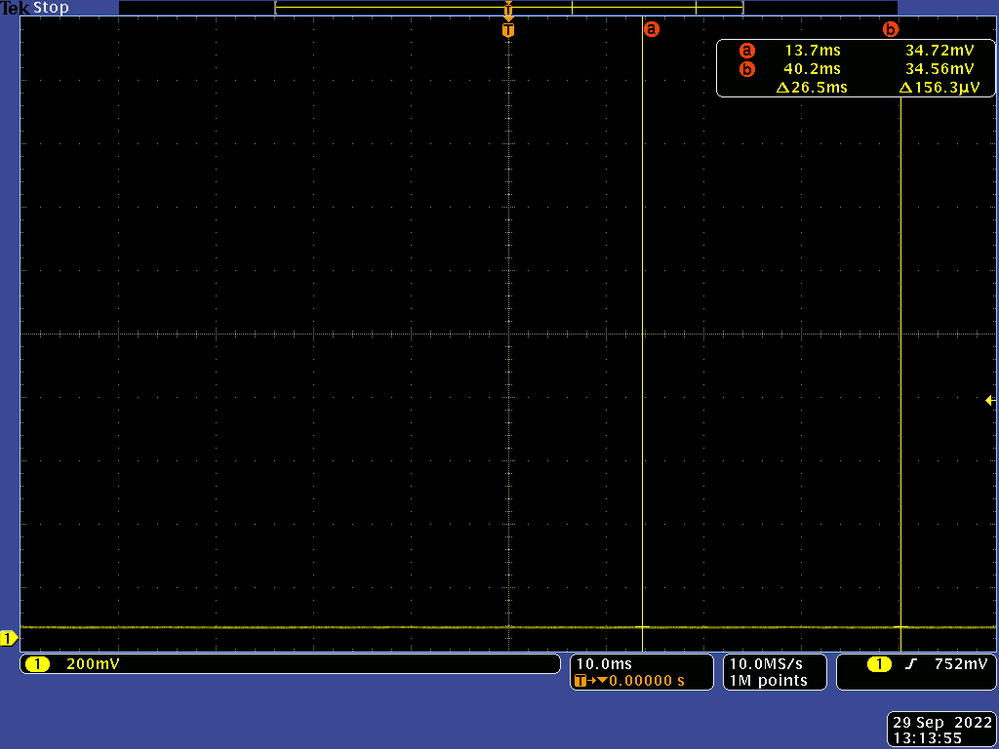

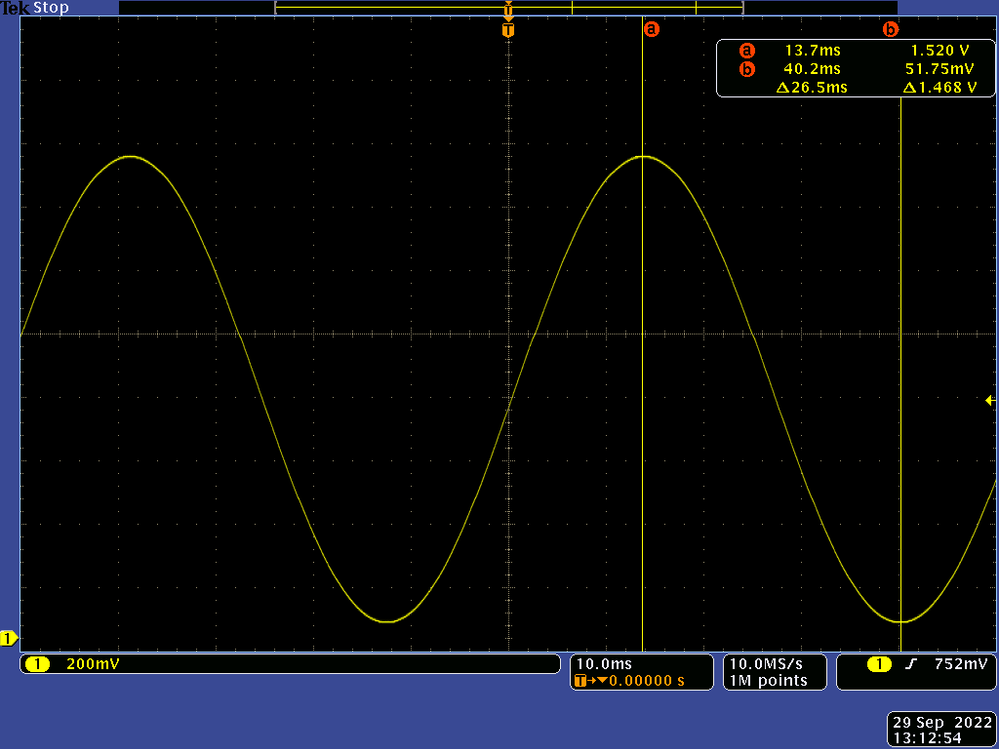

I use the B-U585I-IOT02A, modified VREF+ pin to be powered from internal VREFBUF 1.5V. Then I use the DAC1 to produce a sine wave, it gets quite close to the rails.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-09-29 7:00 AM

Then I sample the signal with the ADC1 from PA4, also using 1.5V as reference voltage using a pretty plain setup (no oversampling etc) and feed it to the MDF.

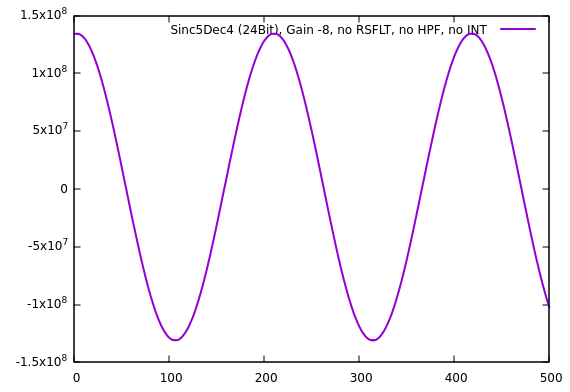

When I use the CIC stage with SINC5 and a decimation of 4, this should result in 24bit wide internal results.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-09-29 7:02 AM

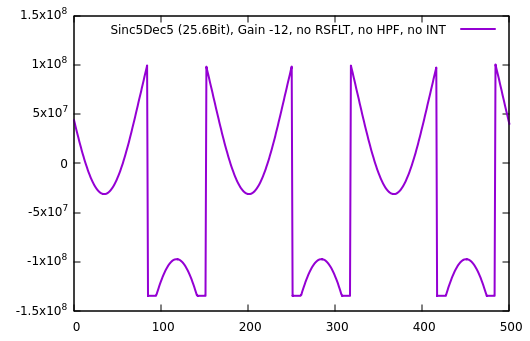

I was not overly surprised, in my CIC simulation playing around with an "internal" width of 26, only 25bits were useful, before it saturated.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-09-29 7:04 AM

There is a little room for improvement by using the correct offset.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-09-30 2:04 AM

@Gwenole BROCHARD I've updated the thread.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-09-30 2:52 AM

Hello @Andreas Köpke,

From your inputs, here are my comments:

- Sinc5 - Dec4 the maximum amplitude read is 1.3e8 which can be represented on 27.9 bits. The maximum value on 24 bits is +/- 8.39e6

- Sinc5 - Dec5, firstly there is an offset in the injected signal. It seems that with a full scale signal (14 bits) + offset a wrap-around occurs.

I will reproduce on my side but I don't expect an issue with the MDF. I come back with further analysis.

Thank you for sharing the details.

Best Regards,

Gwénolé

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-09-30 3:10 AM

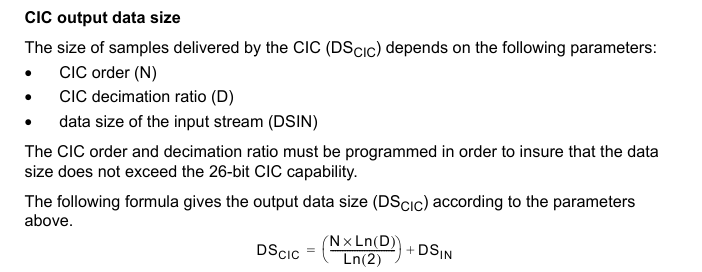

I'm referring to the Reference Manual

RM0456

Reference manual

STM32U575/585 Arm®-based 32-bit MCUs

March 2022, RM0456 Rev 3, page 1239

where it says:

with N = 5, D = 4 and DSin = 14 this results in

DScic = 24

and with N = 5, D = 5 and DSin = 14 this results in

DScic = 25.60964

Both values are within the recommendation DScic < 26bit.