- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: How to check at runtime if a debugger is conne...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to check at runtime if a debugger is connected ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-18 10:24 AM

Hi all !

I would like to know if there is a possibility to check at runtime if a debugger is connected to the STM32.

I have to distinguish between two use cases in software:

- application connected to a debugger via 4 pin header (SWD and power 3.3V / GND) -> no battery protection needed

- appliction is running in normal operation state with connected battery - battery protection (to greater than 3.3V) needed

Any help/hints are appreciated - thanks !

Best regards,

Michael.

#check-debugger-connected-programmatically- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-18 10:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-18 10:46 AM

I have this for my SWV trace, suggest you look at ITM and SCB registers (not Cortex-M0)

if (*SCB_DHCSR & 1) // Debugger Enabled

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ddi0337e/CEGCJAHJ.html

//****************************************************************************

static int Debug_ITMDebug = 0;

//****************************************************************************

void Debug_ITMDebugEnable(void)

{ volatile unsigned int *ITM_TER = (volatile unsigned int *)0xE0000E00; volatile unsigned int *ITM_TCR = (volatile unsigned int *)0xE0000E80; volatile unsigned int *SCB_DHCSR = (volatile unsigned int *)0xE000EDF0; volatile unsigned int *SCB_DEMCR = (volatile unsigned int *)0xE000EDFC;*((u32 *)0xE0042004) |= 0x27;

printf('%08X %08X %08X %08X\n', *ITM_TCR, *ITM_TER

, *SCB_DEMCR, *SCB_DHCSR

);if ((*SCB_DHCSR & 1) && (*ITM_TER & 1)) // Enabled?

Debug_ITMDebug = 1;}//****************************************************************************

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-18 01:10 PM

Thanks for pointing me into the right direction !

I have this for my SWV trace, suggest you look at ITM and SCB registers

(not Cortex-M0)

Unfortunately the target processor is a STM32F072 (Cortex M0) and the detection is not working.

The ARM documentation for Cortex M0 lists the DHCSR register:

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ddi0337e/CEGCJAHJ.html

but there is no detailed description about the bit definitions or the address of the register ...

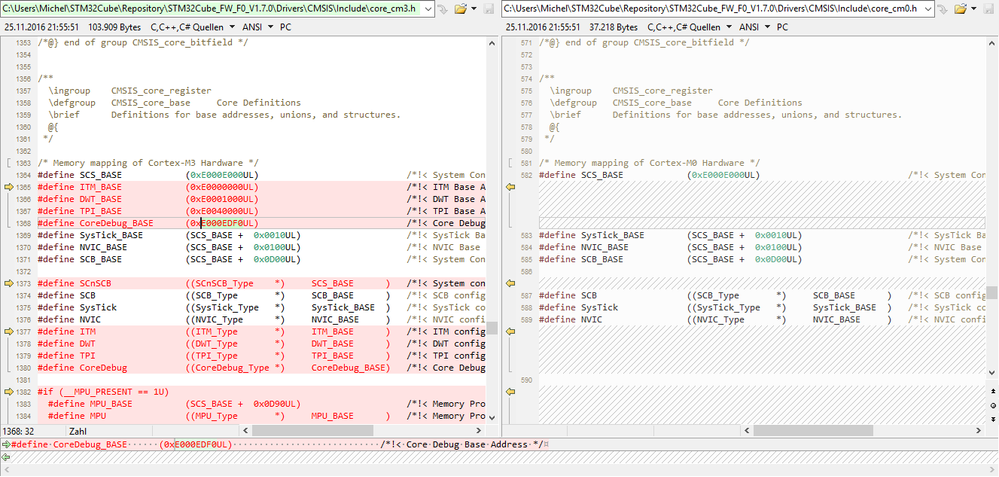

Also the CMSIS register header file shows a lack of the CoreDebug_BASE register

Is this feature simply not available for a M0 device ???

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-18 01:33 PM

>>

Is this feature simply not available for a M0 device ???

They dropped a lot of functionality out, which I've always felt is a step backward, which is why I don't have much time for the M0.

Look at the DBGMCU registers, and the clocks in the AHB/APB enabled at ResetHandler... because the debugger has likely tweaked things to suit its needs.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-18 02:42 PM

A quick implementation does not appears to be quite easy. ...

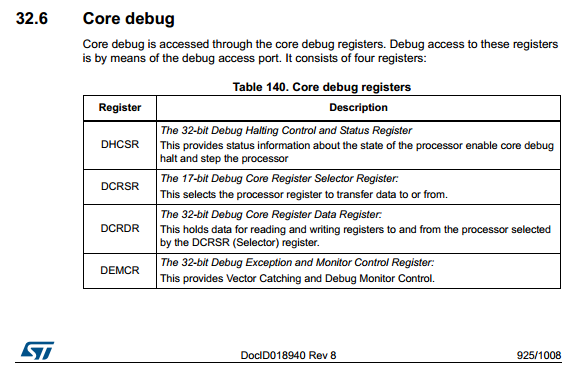

In any case I'm very confused to find a chapter 32.6 Core debug in the

reference manual which are obviously not available:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-18 08:24 PM

I don't know, it is not going too be unduly hard to check a few things...

printf('%08X %08X %08X\n', RCC->AHBENR, RCC->APB1ENR, RCC->APB2ENR);

if (RCC->APB2ENR & RCC_APB2Periph_DBGMCU) puts('DBGMCU Enabled');RCC->APB2ENR |= RCC_APB2Periph_DBGMCU; // Enable so with can readprintf('%08X %08X %08X\n', DBGMCU->CR, DBGMCU->APB1FZ, DBGMCU->APB2FZ);Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-12-13 10:42 AM

katzenberger.michael wrote:

Is this feature simply not available for a M0 device ???

The feature exists - but the register is not accessible to the user code running in the chip.

>:(

See:

- Bricked my custom STM32WB board while changing option bits in STM32 MCUs Wireless

- Custom STSPIN32 Board flashing not working in STM32 MCUs Motor control

- STM32H723: Can't connect to bootloader via UART / at all in STM32 MCUs Products

- Random high write times on SD card with STM32 and FileX in STM32 MCUs Boards and hardware tools

- Code Debugging using STLINKV2 in STM32 MCUs Boards and hardware tools