Help with i2s configuration

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-04-02 3:05 AM

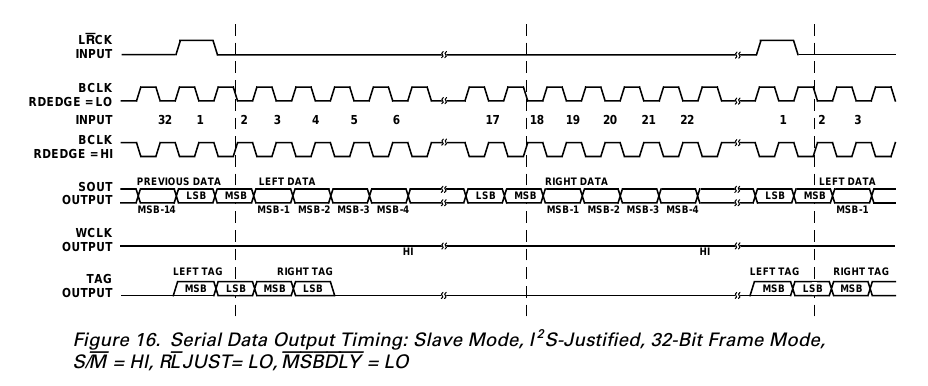

hello everyone

i have adc ad1877, configured as in picture How i should configure i2s in stm32f4 ? I have tried this one I2S_InitStructure.I2S_AudioFreq = I2S_AudioFreq_32k; I2S_InitStructure.I2S_Standard = I2S_Standard_PCMShort; I2S_InitStructure.I2S_MCLKOutput = I2S_MCLKOutput_Enable; I2S_InitStructure.I2S_CPOL = I2S_CPOL_Low; I2S_InitStructure.I2S_DataFormat = I2S_DataFormat_32b; I2S_InitStructure.I2S_Mode = I2S_Mode_MasterRx;also tried few others configurations but with no luck.Sometimes if i manually reset few times adc it works. Maybe it must be special logic of reseting this adc? #i2s #stm32 #dma

How i should configure i2s in stm32f4 ? I have tried this one I2S_InitStructure.I2S_AudioFreq = I2S_AudioFreq_32k; I2S_InitStructure.I2S_Standard = I2S_Standard_PCMShort; I2S_InitStructure.I2S_MCLKOutput = I2S_MCLKOutput_Enable; I2S_InitStructure.I2S_CPOL = I2S_CPOL_Low; I2S_InitStructure.I2S_DataFormat = I2S_DataFormat_32b; I2S_InitStructure.I2S_Mode = I2S_Mode_MasterRx;also tried few others configurations but with no luck.Sometimes if i manually reset few times adc it works. Maybe it must be special logic of reseting this adc? #i2s #stm32 #dma

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-04-04 6:48 AM

Perhaps you have just locked out yourself.

Check the relevant supply voltages on the board, and if o.k., try a mass erase with the Flash Loader Demonstrator, after booting it into system bootloader. There are several threads about this procedure here ...- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-04-05 2:29 AM

Whatever...

In adc datasheet says that reset pulse should be made synchronous to clkin (mcko) . How to make it? By using some interrupt or what?- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-04-05 8:32 AM

In adc datasheet says that reset pulse should be made synchronous to clkin (mcko)

Not really. It says you should do this if you have more than one ADCs and want them all to leave the reset state at the same time. However, I still can't understand the fuzz about a 28-pin, 5V device. Perhaps the signal levels (3.3V <--> 5V) are part of your problems ...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-04-05 11:30 PM

Maybe, next time i'll try ad1871, it has independent power supply for i/o which can be powered from 3 volts

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-04-06 6:19 AM

Seriously, I would consider this 3.3V/5V difference as possible source of your problems.

While the STM32 pins might be 5V tolerant and even read signals correctly, the output signals to the ADC might not reach the L/H theshold. That is a perfect recipe for spurious trouble misbehavior of the ext. device, and lots of new grey hairs. Consider level shifting circuitry, or rather another ADC.- « Previous

-

- 1

- 2

- Next »