- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Help to find a suitable configuration for PWM + CO...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Help to find a suitable configuration for PWM + COMP + DAC

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-04 7:19 AM

Hi community,

I am struggling to find how (or if) is possible to use the TIM1 (advanced control timer) of the STM32FG071 to run a hysteretic current regulator completely in hardware (without relying on software)

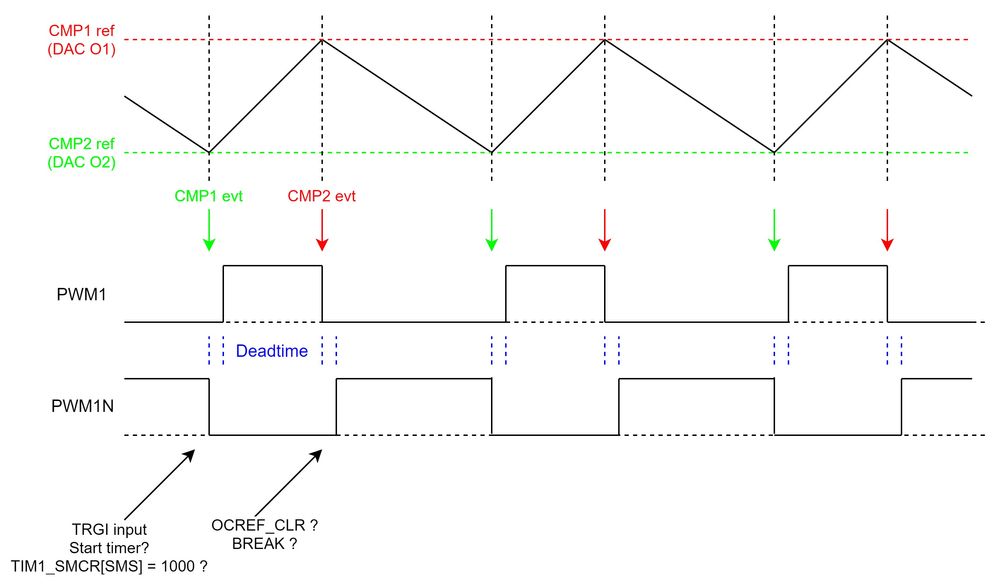

The idea is to use both comparators of the chip together with the 2 values of the DAC to set maximal e minimal current values, and then feed the current signal to the input of both comparators and let this information control the set /reset of the OC1 & OC1N outputs (to also take advantage of the deadtime), therefore controlling both frequency and duty cicle of the output stage.

As shown in this image:

The problem is that the due to the fairly complex control of this timer module and all its possible configurations I am not even able to conclude if it's feasible or not, I've already thought about using One Pulse Mode, OCREF_CLR, Gated mode and Break inputs, but the more I read the more complex it gets..

My question goes to the ones that are already experienced with the advanced parts of this timer, is this idea feasible? if yes, which features should I combine to put it to work?

OPM + OCREF_CLR ?

OPM + BRK ?

TRGI + OCREF_CLR ?

TRGI + BRK ?

what else could work ?

Thank you all in advance

Best Regards

Gustavo

- Labels:

-

COMP

-

DAC

-

STM32G0 Series

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-07 3:09 AM

Hi Jan,

You are absolutely right, the period of CH1 is 591.5us (can also be seen in the preivous image, Prod(C1)))

Here is the output of of TM1 CH2 in PWM mode (in blue), and seems to be happening exactly what you said, the timer is indeed reset when the COMP1 goes up:

Thanks for it!

Lets see ST answer..

BTW, why you say we should avoid using Break? what are the downsides of it?

Now it seems to be my only option...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-07 4:44 AM

Break is intended as a last-resort safety feature, so maybe that's less appropriate for cycle-to-cycle control. But maybe it would work, if you set BDTR.AOE and .OSSI, in conjunction with properly set CR2.OIS1/OIS1N... Well, try...

Maybe one more way to comtemplate would be to

- leave the COMP2->OCREF_CLR path as it is now

- set COMP1->ETRF->TRGI and RESET mode as it is now

- set CH1 in CCMR to PWM2, *don't* enable counter i.e. leave CR1.CEN=0

- set CCMR1.OC1FE=1

JW

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-07 5:55 AM

Right, I got it working as intended with break after configuring AOE, OSSI, OIS1 and OIS1N, but I understand what you mean, when we use break for this control we have no ways of stopping all the outputs in the hardware if anything goes wrong...

This second way you suggested is also partially working, I tested here and it will turn on and off as intended, but it is never starting by itself, I need to first inject an external signal to the comparator input to make it start switching, I also tried generating EGR.UG and EGR.CC1G, but not worked.. the only way was injecting a 3V signal to the comparators input..

And there is also the downside of not being able to set a minimum operating frequency and a maximum dutycicle value, as the timer is not running

I also thought about using one DMA channel triggered by the COMP1 to copy the actual timer counter to the OC1, just to avoid hitting this bug, but seems to be a really resource expensive and ugly quick fix

Thanks again for your help and expertise, and just out of curiosity, do you work for ST?

You understand a lot about these micros..

Gustavo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-07 8:15 AM

> This second way you suggested is also partially working, I tested here and it will turn on and off as intended, but it is never starting by itself

You can set OC1REF manually by setting briefly CCMR1.OC1M to Force Active Level, then setting it back to PWM2.

> And there is also the downside of not being able to set a minimum operating frequency and a maximum dutycicle value, as the timer is not running

You probably *can* run the timer, I just did not want an unnecessary distraction for the first experiment. Note, that without input from the comparators, in PWM2 mode the output gets "naturally" cleared upon reset and set upon compare match, so maybe you want to draw timing diagrams to understand the various scenarios which might happen.

When the timer runs, you can also maybe employ some of the Combined modes with other channels to generate more complex waveforms.

> just out of curiosity, do you work for ST?

No, I am just a user of STM32. That, I guess, makes ST working for me... ;)

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-11 12:35 AM

Now I understood what is happening using PWM2 and OCREF_CLR, thanks !

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-11 12:38 AM

That's one option, I will see with which mode we will go forward, thanks again Jan for all your help!

And lets hope ST correct it in the next chip revision :)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-13 1:51 AM

So, more than a month and we still don't have a response from ST!

I at least want to see what ST has to say and what kind of solutions they will suggest.

Should I open a ticket for it? what is the correct way of reporting it?

@Vincent Onde

@Imen GH

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-13 10:02 AM

> Should I open a ticket for it?

Probably yes. This is, after all, just a forum...

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-16 4:07 AM

Hi Jan, I just opened a ticket, thanks.

Gustavo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-19 10:27 AM

Hello Gustavo, @Community member ,

Sorry for the delay replying it to you.

We have checked this and do confirm this is a bug, as Jan guessed. It is present since the very beginning of STM32s (all timer revisions are impacted), and it will be fixed in next one.

Here-below is the description that will be published in the errata sheets to come.

But basically you worked this out by yourselves and found the best work-around. Congratulations.

Best regards,

Vincent

Description

The output compare clear event (ocref_clr) is not correctly generated when the timer is configured in the following

slave modes: Reset mode, Combined reset + trigger mode, and Combined gated + reset mode.

The PWM output remains inactive during one extra PWM cycle if the following sequence occurs:

1. the output is cleared by the ocref_clr event

2. the timer reset occurs before the programmed compare event

Workaround

Apply one of the following measures:

1. Use BKIN (or BKIN2 if available) input for clearing the output, selecting the Automatic output enable mode

(AOE = 1).

2. Mask the timer reset during the PWM ON time to prevent it from occurring before the compare event (for

example with a spare timer compare channel open-drain output connected with the reset signal, pulling the

timer reset line down).

- IPM30B: minimal working setup in STM32 MCUs Motor control

- Question about VBUS behavior in STM32 USB OTG and impact of externally supplied VBUS in STM32 MCUs Products

- Multi protocol communication shield (Nucleo ZIO & Arduino Uno V3 compatible) in Others: STM32 MCUs related

- STM32WB05N: Unable to connect to CubeProgrammer (No STM32 target found) in STM32CubeProgrammer (MCUs)

- STM32N6 DK 570: Binary Signing & Header Alignment Required for Successful Boot in STM32CubeIDE (MCUs)