- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Hal stm32f103 and dds problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Hal stm32f103 and dds problem

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-06-19 03:11 AM

i have problem with data ud and clk signals out to dds.

its not a steady stream to dds.

in the oscilloscope the data,clk ud signals are not stable.

the signal are moving and jumping around so the dds of course gives weird and wrong freq.

i tried internal and external rcc.

my question is, if anyone had a similiar problem with sending data and clk stream and its a weird output flow, so you can relate to my problem and maybe suggest something to look for?

it must be some settings to change.

something simple i dont understand....

- Labels:

-

STM32F1 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-06-19 05:45 AM

And we are going to need WAY more information. How do you have the F103 connected to the DDS chip? Parallel interface? SPI? I2C? How are you generating the signals to the DDS? Show us the relevant code (initialization and writing data to the DDS)? How about screen captures of the scope traces?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-06-19 11:04 AM

yes sure. :)

f103 is connected to dds as serial.

so i use GPIO_speed 2Mhz. (max for dds is 3Mhz)

GPIO_Mode_Out_PP

no pull-up and no pull-down. (i havnt tried to changed that... will try that tomorrow)

tried gpio output level both high and low.

connection to dds is easy, data - data , clk to clk, ud - ud...

nothing can go wrong there.

the dds code i use has before worked fine when used by coide.

now i use Hal so the code looks like this.

void ad_Init()

{

HAL_GPIO_WritePin(clk_GPIO_Port, clk_Pin, GPIO_PIN_SET);

HAL_GPIO_WritePin(ud_GPIO_Port, ud_Pin, GPIO_PIN_SET);

HAL_GPIO_WritePin(data_GPIO_Port, data_Pin, GPIO_PIN_SET);

HAL_GPIO_WritePin(clk_GPIO_Port, clk_Pin, GPIO_PIN_RESET);

HAL_GPIO_WritePin(ud_GPIO_Port, ud_Pin, GPIO_PIN_RESET);

HAL_GPIO_WritePin(data_GPIO_Port, data_Pin, GPIO_PIN_RESET);

}

void ad_SetFreq()

{

int n=0;

long frequency = 0x1CAC0831; //0x0A3D70A4; 5MHz

for (n=0; n<32; n++)

{

if ((frequency & 0x01) == 1)

{

HAL_GPIO_WritePin(data_GPIO_Port, data_Pin, GPIO_PIN_SET);

}

else

{

HAL_GPIO_WritePin(data_GPIO_Port, data_Pin, GPIO_PIN_RESET);

}

HAL_GPIO_WritePin(clk_GPIO_Port, clk_Pin, GPIO_PIN_SET);

HAL_GPIO_WritePin(clk_GPIO_Port, clk_Pin, GPIO_PIN_RESET);

frequency>>=1;

}

HAL_GPIO_WritePin(data_GPIO_Port, data_Pin, GPIO_PIN_RESET);

for (n=0; n<8; n++)

{

HAL_GPIO_WritePin(clk_GPIO_Port, clk_Pin, GPIO_PIN_SET);

HAL_GPIO_WritePin(clk_GPIO_Port, clk_Pin, GPIO_PIN_RESET);

}

HAL_GPIO_WritePin(ud_GPIO_Port, ud_Pin, GPIO_PIN_SET);

HAL_GPIO_WritePin(ud_GPIO_Port, ud_Pin, GPIO_PIN_RESET);

}- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-06-19 11:27 AM

How about a shot of the oscilloscope screen showing what you are seeing on the clock & data signals?

> the dds code i use has before worked fine when used by coide.

> now i use Hal so the code looks like this.

Maybe different optimization settings between what CoIDE used and what you are now using? Or newer/different versions of the ARM GCC compiler that optimize differently? Or different (shorter?) code in HAL than whatever you were using before (STL would be my guess from CoIDE).

What frequency are you running the F103 at? If you are running at 72MHz, it is possible that your calls to toggle the clock pin are creating too narrow a clock pulse (if indeed a 3 MHz clock period is the shortest the DDS can accept). Likewise, you may need a higher drive current on your GPIO than the "2 MHz" setting, unless you slow your clock down.

As a very rough test, add HAL_Delay(1) calls between your clock "set" and clock "reset" function calls. This will REALLY slow things down.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-06-19 12:22 PM

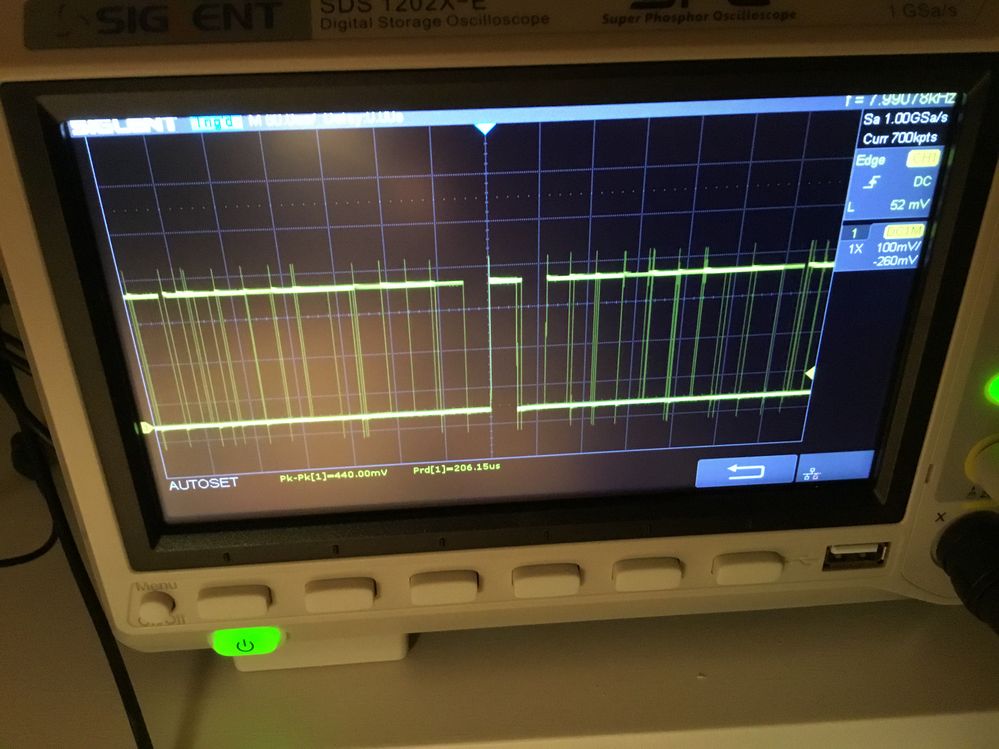

First picture is datastream from f103.

As you see its going crazy.

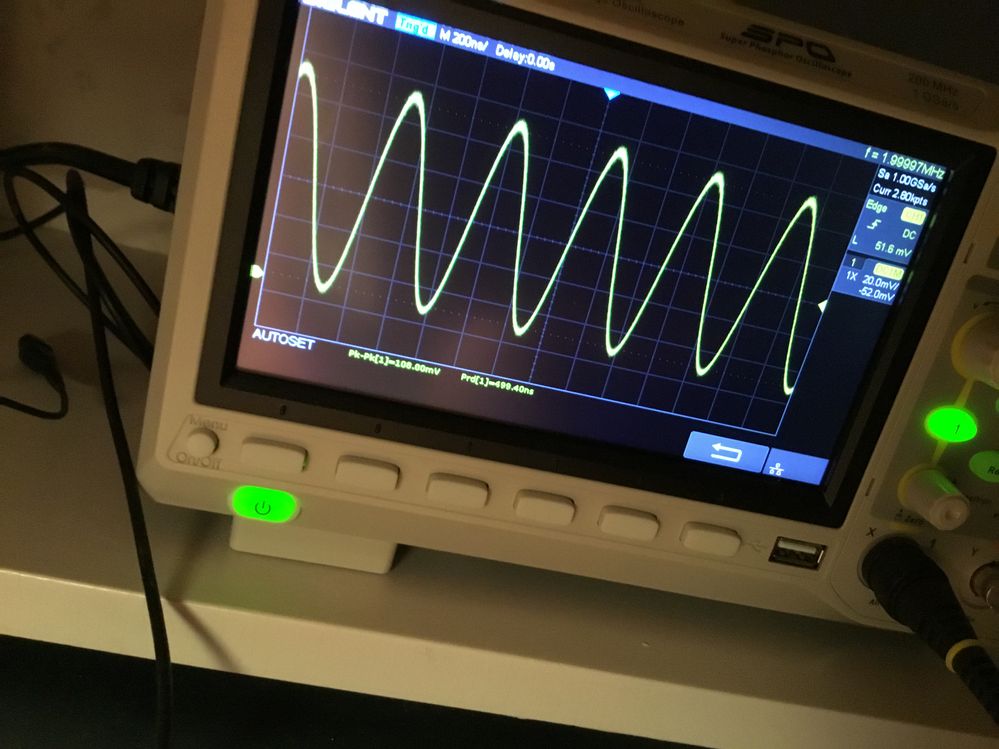

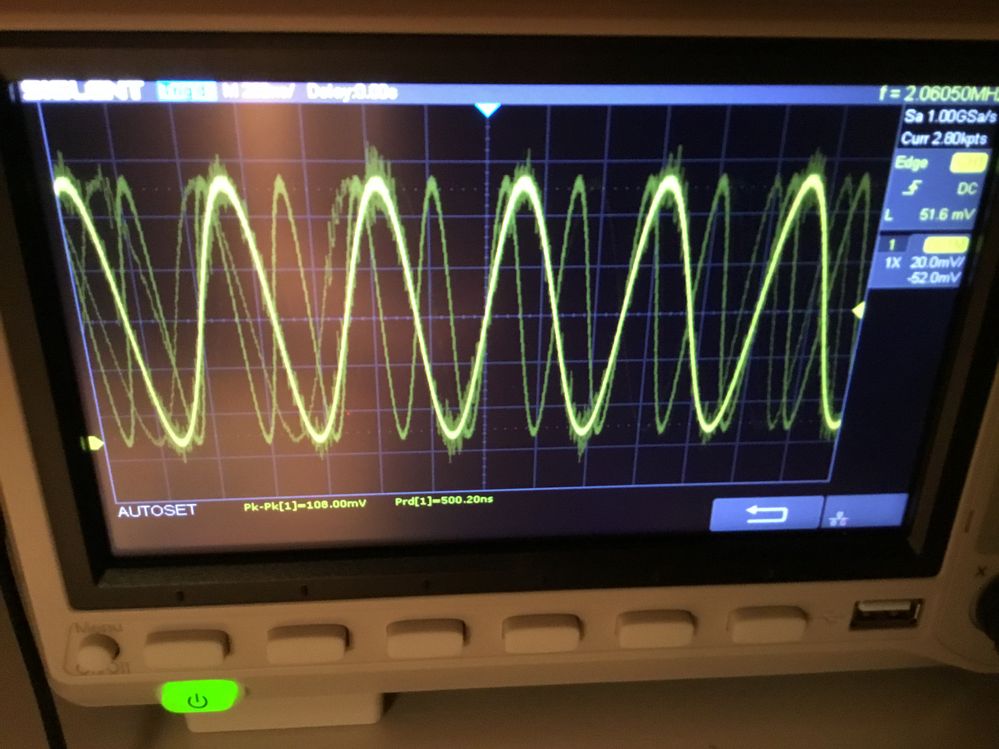

the next two photos is dds out...

i have programmed it to run on 4Mhz.

its weird, as you can see you have 2Mhz and some more frequensies but When i push down reset- Button on f103 its a steady 2Mhz signal... exactly the half frequency i have programmed.

so strange.

I Will try a delay as you suggestiv tomorrow.

tnx for givning me some thought and ideas to try out...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-06-20 06:33 AM

Your first scope image only shows 1 trace - should we presume that is the clock signal to the DDS? And that looks like you have the scope running continually and further more you keep re-sending the (same?) data over and over again. Is that what is happening? That could also help explain why the DDS output signal is jumping around while the CPU is running, and generates a stable waveform when you hold the CPU in reset.

You are sending 40 bits total, with the first 32 bits being the frequency data, send LSB first. Is that what the DDS is supposed to take? Which DDS chip are you using?

I am also not sure what time scale you scope is using. It looks like text at the bottom of the screen says "Prd[1] = 206.1us", so the scope thinks the period of the (clock???) signal is 206us (roughly 5KHz). That sounds very slow given the code you show, unless you are running the CPU at much less than 72 MHz. Which brings me back to one of my original questions - what is the F103's clock frequency?

Can you show 2 traces, one with clock and one with data, And only send the data one time?

- STM32H753 SDMMC in SDIO mode producing repeated DATEND interrupt without new request in STM32 MCUs Embedded software

- STM32WL5MOC EXTI and STOP2 in STM32 MCUs Wireless

- Output Compare Register update in stm32 in STM32CubeMX (MCUs)

- STM32U575ZIQ SPI behavior when enabling while slave select signal and clock are active? in STM32 MCUs Products

- IOC file working in v6.12.1 gives "Not a valid ioc" in v6.13.0 in STM32CubeMX (MCUs)