- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- FMC synchronous non-multiplexed PSRAM clock spikes...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FMC synchronous non-multiplexed PSRAM clock spikes when writing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-13 6:55 AM

Hello

We are using FMC for communication with FPGA. FPGA has memory-mapped periphery implemented in compatible mode for synchronous non/multiplexed PSRAM/NOR.

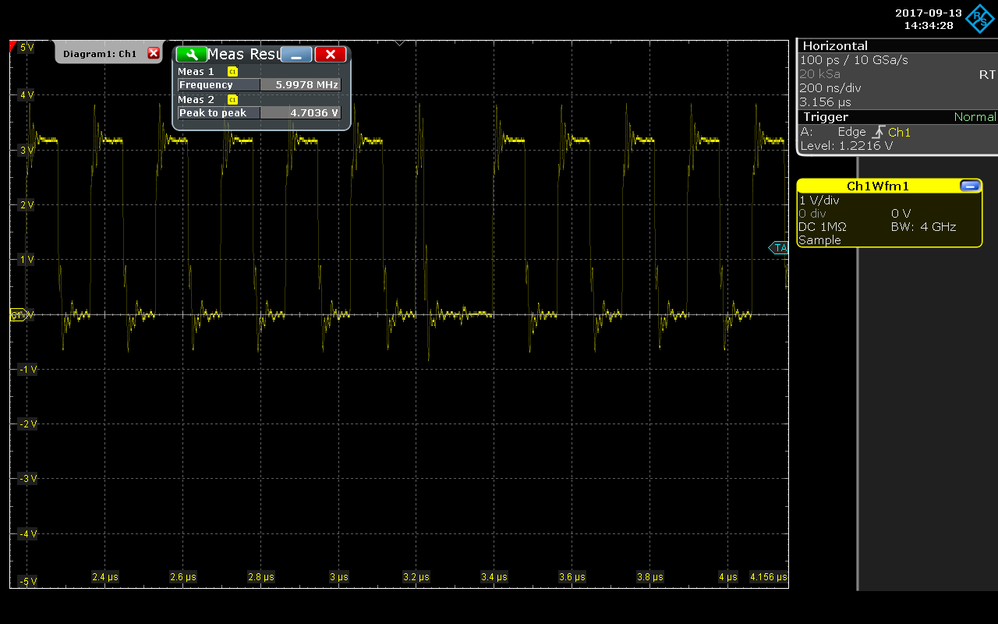

We are facing problem with misinterpreted spikes/cut pulses in CLK signal at higher frequencies (see pictures below).

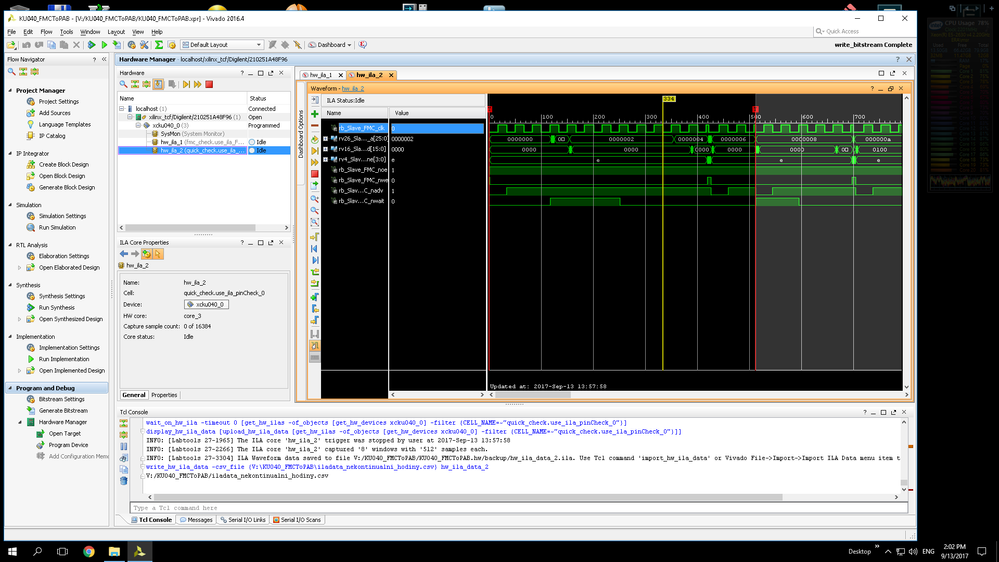

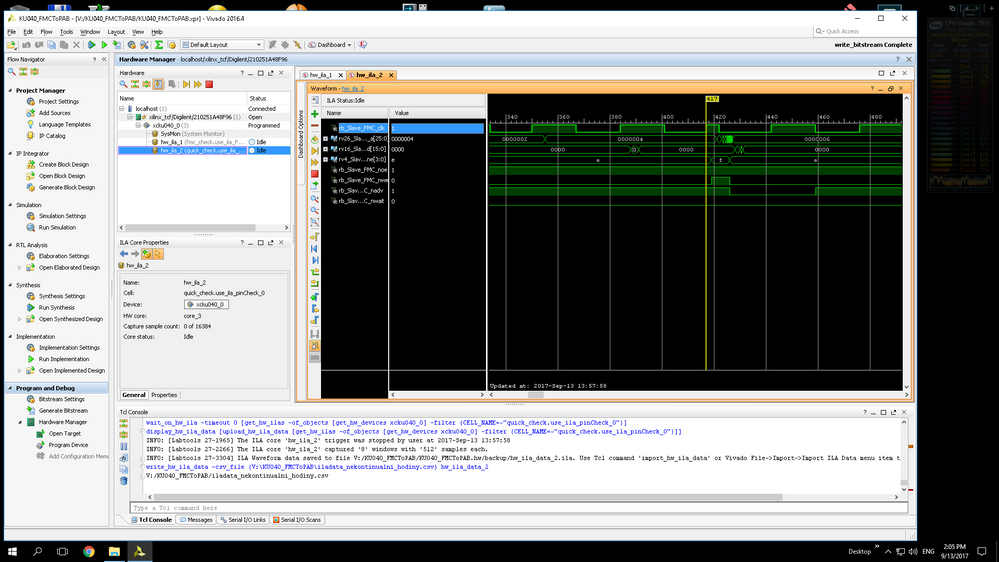

These are screenshots of ILA blocks (logic analyzers in FPGA). It shows how bus is interpreted and seen by logic in FPGA.

detail...

It seems that these ''cut'' CLK pulses shows before NWE signal is toogled. Also this only happens when we write data...not when reading from memory.

It is can be fw/hw bug or it is a feature of MCU?

Used MCU: STM32F767ZI

FCLK 96MHz

FMC configuration

FMC CLK 6MHz (FMC div 16), continuous

Timing.AddressSetupTime = 15;

Timing.AddressHoldTime = 15; Timing.DataSetupTime = 255; Timing.BusTurnAroundDuration = 15; Timing.CLKDivision = 16; Timing.DataLatency = 2; Timing.AccessMode = FMC_ACCESS_MODE_A;Memory type PSRAM

Address 24bits

Data 16 bits

Clock Burst Read Write

Address valid signal enabled

NWAIT signal enabled

Regards,

Daniel

#psram #fmc #clock-spikes- Labels:

-

FMC-FSMC

- Bare Metal ADC on NUCLEO-H745ZI-Q in STM32CubeIDE (MCUs)

- Feel confused about "USART with SPI" in datasheet of STM32G0B1RE in STM32 MCUs Products

- Notes on STM32 (G431) USB-CDC throughput (libusb) and pitfalls of using dd to transfer data (I2S) in STM32 MCUs Products

- Readout external ADC by SPI doesn't work correctly in STM32CubeIDE (MCUs)

- STM32H745, faultily write access to external memory over debugger in STM32 MCUs Products