- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: External SRAM access using FMC (STM32f439zi) -...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

External SRAM access using FMC (STM32f439zi) - How to connect unused pins?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-05-23 05:34 PM

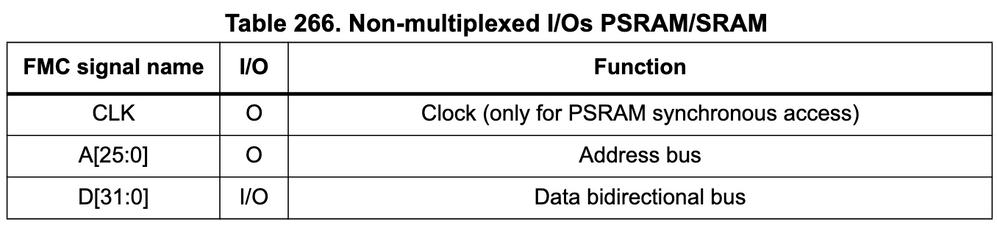

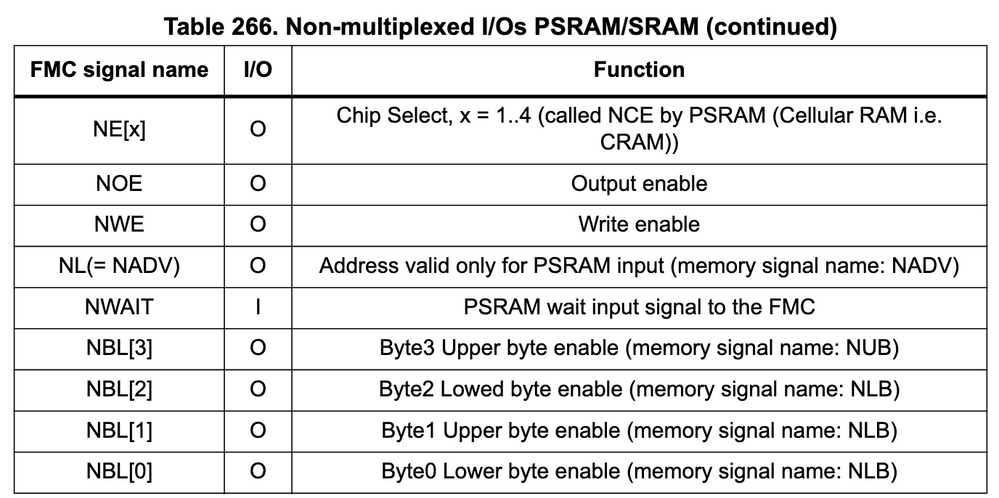

I am trying to interface a Nucleo-f439zi board with an external AS6C4008-55SIN SRAM chip through an "Arduino HAT" style board I am working on. Below is my current schematic.

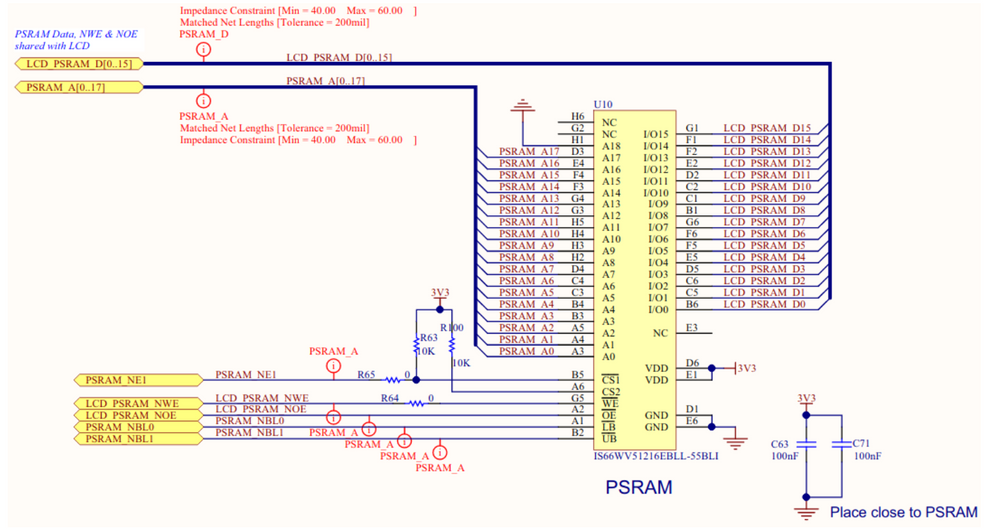

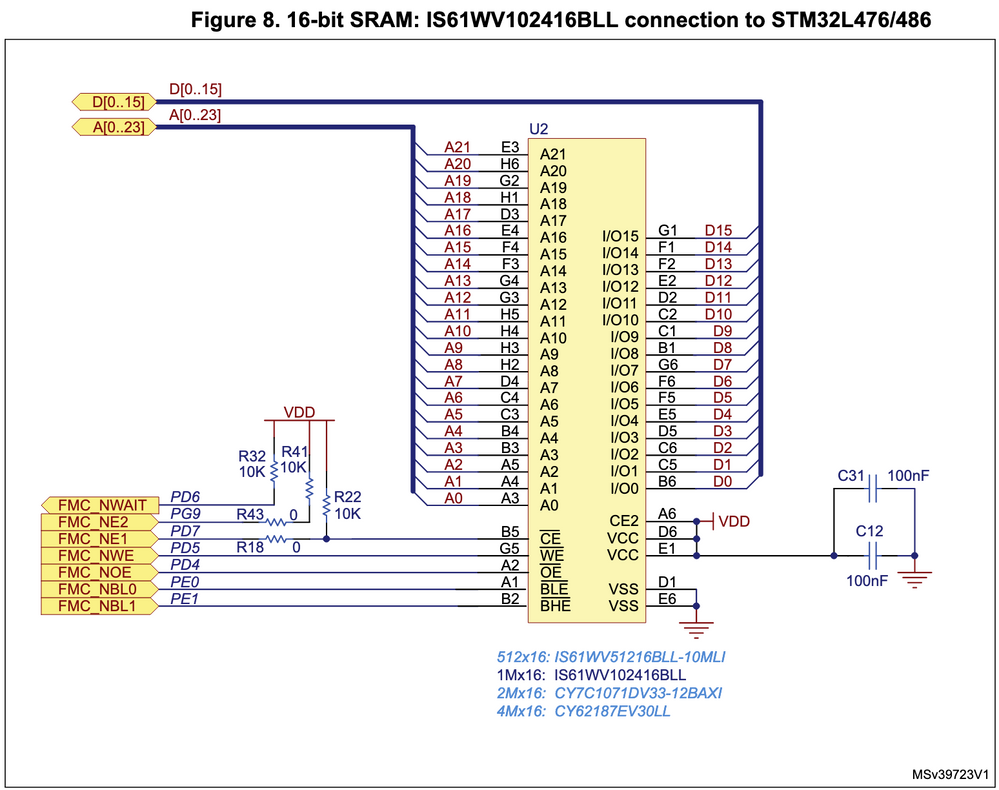

I based my schematic on two other examples for STM32 chips different than the one I'm using:

One from a blog post pertaining to a development board which already comes with an external SRAM chip: vivonomicon dot com/2020/07/26/bare-metal-stm32-programming-part-11-using-external-memories/

And the second one from an ST reference document:

www dot st dot com/resource/en/application_note/an4761-using-stm32l476486-fsmc-peripheral-to-drive-external-memories--stmicroelectronics.pdf

My questions:

Should I connect Vcc to STM32's 3V3 or to Vdd?

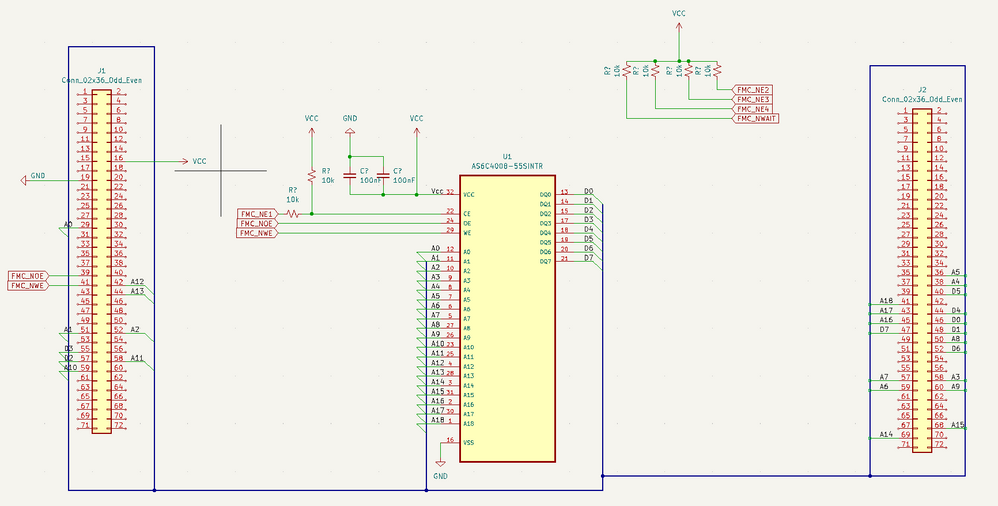

Why connect FMC_NE[2..4] and FMC_NWAIT to Vcc through 10k resistors? (I understand the N letter means high = disabled, but why 10k resistors? To limit current?)

What should I do with FMC_NBL[3..0]?

How many STM32 ground pins should I be connecting to? Is one enough, or should I use all of them?

FMC_clock, and NL I assume are not used, as in the other examples presented.

Should I worry about trace impedance and length? I see one of the presented examples considers this, but I have no clue how they determined those values. Neither the MCU nor the SRAM manual/datasheet show any such values.

- Labels:

-

FMC-FSMC

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-08-26 09:49 AM

>>Why connect FMC_NE[2..4] and FMC_NWAIT to Vcc through 10k resistors? (I understand the N letter means high = disabled, but why 10k resistors? To limit current?)

To establish a known/safe state before all the pins/interfaces have been brought up. Low current vs driven-low state.

Also allows for different parts to be brought up independently of each other without clashing on the bus.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-08-26 10:36 AM

Thank you @Community member

I can understand that, but then why aren't FMC_NWE, FMC_NOE, and so on, also connected in the same way?

- STM32F439ZI ETHERNET TCP CONNECTION in STM32CubeIDE (MCUs)

- Nucleo-G474RE couldn't establish qspi connection with external Flash W25Q16JV in STM32 MCUs Products

- ST-Link V3 not detected in Mac M2 in STM32 MCUs Boards and hardware tools

- Issue raised in dual core debugging while adding images in the external sdram memory in STM32 MCUs Products

- ST-Link can't connect to STM32H750VB in STM32 MCUs Products