Derive an exact timer rate from PLL

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-30 11:46 AM

Hello,

I am working with the STM32L486 chipset and we need to generate an exact 38400Hz timer. Currently we have a 5MHz or 25MHz external clock coming in but the PLL clock tree does not seem to favor getting the exact 38400Hz rate for a timer. Is it possible with the above external clock rates? or if not, any suggestions to get this, including a different rate for external clock source?

Thanks,

ED

Note: this post was migrated and contained many threaded conversations, some content may be missing.Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-30 12:32 PM

At 12 MHz input clock you can run CPU at 24, 48 or 72 MHz

I believe an input of 4, 8 MHz would also offer these. An input of 24 MHz would provide for multiple additional options ranging from 19.2 thru 76.8 MHz

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-30 12:32 PM

At 12 MHz input clock you can run CPU at 24, 48 or 72 MHz

I believe an input of 4, 8 MHz would also offer these. An input of 24 MHz would provide for multiple additional options ranging from 19.2 thru 76.8 MHz

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-30 4:33 PM

Thanks Clive One! I found a crystal at 19.2MHz available that would also do the job.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-10 12:10 PM

Hi Clive One, for my own exercise, I revisited this thread to play around with the numbers in Cube's Clock Configuration and I couldn't seem to get the 24MHz input crystal to output 19.2MHz or 76.8MHz as you stated here. Can you elaborate on how to get to, say the 19.2MHz from a 24MHz input, as an example? Sorry to bring this up again!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-10 12:35 PM

I don't use Cube, I'm a mechanic, the fitter threw out these values

freq=24.0000 MHz

cpu= 19.2000, pll_m= 5, pll_n= 16, pll_p=4, pllcomp=4.800000

cpu= 19.2000, pll_m= 5, pll_n= 24, pll_p=6, pllcomp=4.800000 cpu= 19.2000, pll_m= 5, pll_n= 32, pll_p=8, pllcomp=4.800000 cpu= 76.8000, pll_m= 5, pll_n= 64, pll_p=4, pllcomp=4.800000Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-10 1:03 PM

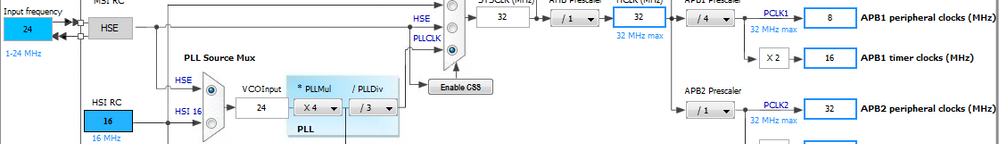

Maybe I am missing something here but not sure if your fitter adheres to the clock tree specified by ST for a particular part, as shown below. How are the pll_m, pll_n, pll_p and pll_comp translating to the PLLMul, PLLDiv, AHB prescaler and APB1 prescaler, etc.?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-10 1:21 PM

Look at the RCC tree in RM.

M is the PLL prescaler. N is the multiplier - for some reason ST omitted that from the 'L4 RM picture; look into the same picture e.g. in RM0090. P is the postscaler - in the L4 that particular postscaler is used for a different purpose and R is used instead for SYSCLK output, again look into RM0090 for the 'original'.

pll_comp obviously is the PLL input frequency; you have to check that (and the PLL output freq too) against the PLL range given for particular chip in DS.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-10 1:31 PM

The AHB/APB stuff is irrelevant, I went from the Reference Manual, and Data Sheet values for the VCO frequencies, and PLL comparison frequencies

Look at what Cube spits out for

HAL_RCC_OscConfig() boiler plate, and tune manually.

&sharpifdef USE_STM32L4XX_NUCLEO

/** * @brief System Clock Configuration * The system Clock is configured as follow : * System Clock source = PLL (MSI) * SYSCLK(Hz) = 80000000 * HCLK(Hz) = 80000000 * AHB Prescaler = 1 * APB1 Prescaler = 1 * APB2 Prescaler = 1 * MSI Frequency(Hz) = 4000000 * PLL_M = 1 * PLL_N = 40 * PLL_R = 2 * PLL_P = 7 * PLL_Q = 4 * Flash Latency(WS) = 4 * @param None * @retval None */void SystemClock_Config(void){ RCC_ClkInitTypeDef RCC_ClkInitStruct = {0}; RCC_OscInitTypeDef RCC_OscInitStruct = {0};/* MSI is enabled after System reset, activate PLL with MSI as source */

RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_MSI; RCC_OscInitStruct.MSIState = RCC_MSI_ON; RCC_OscInitStruct.MSIClockRange = RCC_MSIRANGE_6; RCC_OscInitStruct.MSICalibrationValue = RCC_MSICALIBRATION_DEFAULT; RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON; RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_MSI; RCC_OscInitStruct.PLL.PLLM = 1; RCC_OscInitStruct.PLL.PLLN = 40; RCC_OscInitStruct.PLL.PLLR = 2; RCC_OscInitStruct.PLL.PLLP = 7; RCC_OscInitStruct.PLL.PLLQ = 4; HAL_RCC_OscConfig(&RCC_OscInitStruct);/* Select PLL as system clock source and configure the HCLK, PCLK1 and PCLK2

clocks dividers */ RCC_ClkInitStruct.ClockType = (RCC_CLOCKTYPE_SYSCLK | RCC_CLOCKTYPE_HCLK | RCC_CLOCKTYPE_PCLK1 | RCC_CLOCKTYPE_PCLK2); RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK; RCC_ClkInitStruct.AHBCLKDivider = RCC_SYSCLK_DIV1; RCC_ClkInitStruct.APB1CLKDivider = RCC_HCLK_DIV1; RCC_ClkInitStruct.APB2CLKDivider = RCC_HCLK_DIV1; HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_4);}&sharpendifUp vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-10 1:38 PM

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-10 1:44 PM

Well pll_comp is my computation for the comparison frequency (needs to be in range 4-16 MHz), there's not really a 'multiplier' it divides down the VCO frequency so that VCO / PLL_N == HSE / PLL_M, and pumps the VCO frequency up/down a tad to tune it.

Up vote any posts that you find helpful, it shows what's working..