- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

DDS DAC

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-08-07 10:49 PM

Hello,

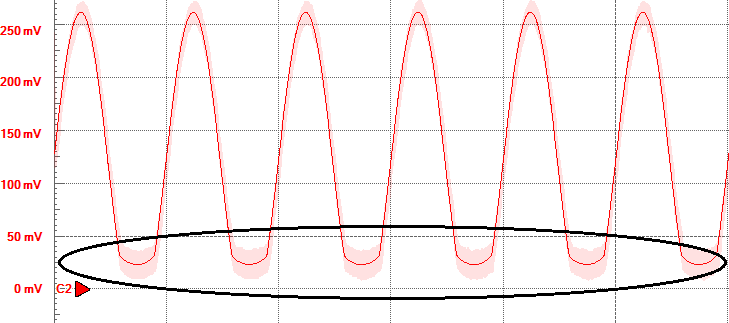

I am generating a sine wave by DDS method, but I dont know why the signal is flattering at the bottom. Does anyone have any idea why is this happening. Thanks #stm32 #dac

Thanks #stm32 #dac

- Labels:

-

DAC

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-08-08 07:32 AM

Look in the DAC section in the data sheet for your device. You will probably find that the DAC buffer amplifier is not rail to rail. The same problem will exist if the output is programmed to go to VRef+.

An unbuffered output can come closer to the rails, but the current drive is meager, usually requiring input to the high impedance pin of an external op amp. Cheers, Hal- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-08-08 11:50 AM

Great that was helpful.... :)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-08-08 12:02 PM

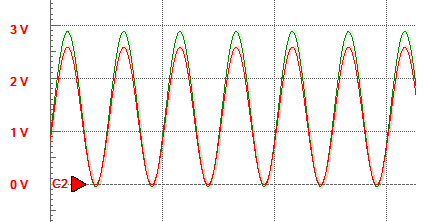

But now there seems a problem that 1 DAC is giving a 300mv lower output that the other for the same signal.

Regards- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-08-08 01:33 PM

Can't help much without more information. What is each DAC driving? Are you using bufferred or unbufferred output? What is the processor ? Are you using a development or discovery board ?

Think about what information you would need if you were asked to answer your question. Cheers, Hal- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-08-08 04:32 PM

Thanks again,

I am using the STM32F4 discovery board. I am using unbuffered for both the DACs. I am just probing at the pins no buffered input or output going to any pin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-08-08 05:10 PM

Life can be very mysterious when you don't Read The Fine Manual.

Table 5 in the F4 Discovery User Manual shows PA4 and PA5 connected to onboard peripherals. Cheers, Hal- sprintf with %f creating problem in STM32 MCUs Products

- Bricked my custom STM32WB board while changing option bits in STM32 MCUs Wireless

- HSE Clock for CAN in STM32 MCUs Products

- STM32WPAN advertising data dynamic update in STM32 MCUs Wireless

- Missing data written to the high-cycle data flash of the STM32H563 in STM32CubeIDE (MCUs)