Can SRAM1, SRAM2, SRAM3 be treated as one continuous memory region?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-26 12:30 PM

(This is regarding STM32H75x)

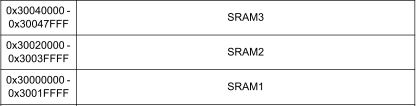

SRAM1, SRAM2, and SRAM3 are separate in the memory map, but they are continuous - there are no gaps between them:

Can they be treated as continuous with respect to the linker, for example:

RAM_D2 (xrw) : ORIGIN = 0x30000000, LENGTH = 288KAnd then place some arbitrary data in that region?

Like, can we place an array that is 288k in that region and use it as a heap, or will bad things happen at the region where SRAM1 ends / SRAM2 starts, etc?

- Labels:

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-12 9:56 AM

I feel like there is a simple answer to this but I haven't been able to find it...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-12 10:01 AM

From the processors perspective they look/appear contiguous.

From and DMA/BUS perspective they might be treated differently, you'd have to review in the context of the bus matrix diagrams

Clocks should also be enabled.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-12 10:29 PM

To use as heap, they're contiguous and the linker doesn't care what they, read https://sourceware.org/binutils/docs/ld/MEMORY.html#MEMORY.

SRAM123 (rw) : ORIGIN = 0x30000000, LENGTH = 0x48000Otherwise find your part's RM and other resources, e.g. AN4891, at https://www.st.com/content/st_com/en/search.html.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-13 3:06 PM

If this is relevant for your application, test whether multi-byte writes over the boundary of the RAMs don't cause trouble.

For example: *(uint32_t *)(0x3003FFFF) = 0x12345678; *(uint32_t *)(0x3001FFFE) = 0x12345678;

-- pa

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-15 8:19 AM

Thanks everyone.

One interesting thing: I did not realize that clocks had to be enabled for these SRAM blocks, and I was somehow using them just fine without those clocks enabled.

I am not sure how... but I have added the clock init in.