- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: 2019 STM32 Wish List

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

2019 STM32 Wish List

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-12-31 06:07 AM

Dear Community Members & STM32 fans,

Let’s end 2018 thanking you for your involvement in our Community and wishing you all the best for 2019!

As already done in 2017 (https://community.st.com/s/feed/0D50X00009bLPmvSAG) and in 2018 (https://community.st.com/s/feed/0D50X00009bLSAKSA4), we open this space to hear from you.

This is an opportunity for us to evaluate what we deliver as offer and to know your expectations.

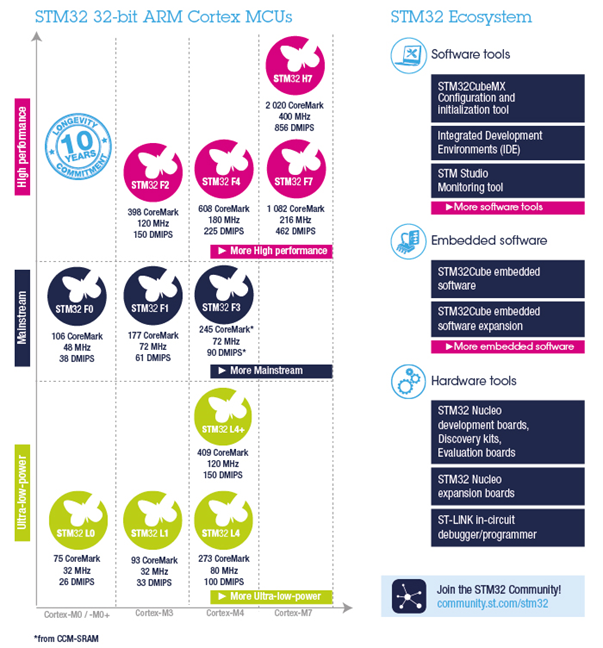

If we come back to the STM32 portfolio end of last year, it was like this:

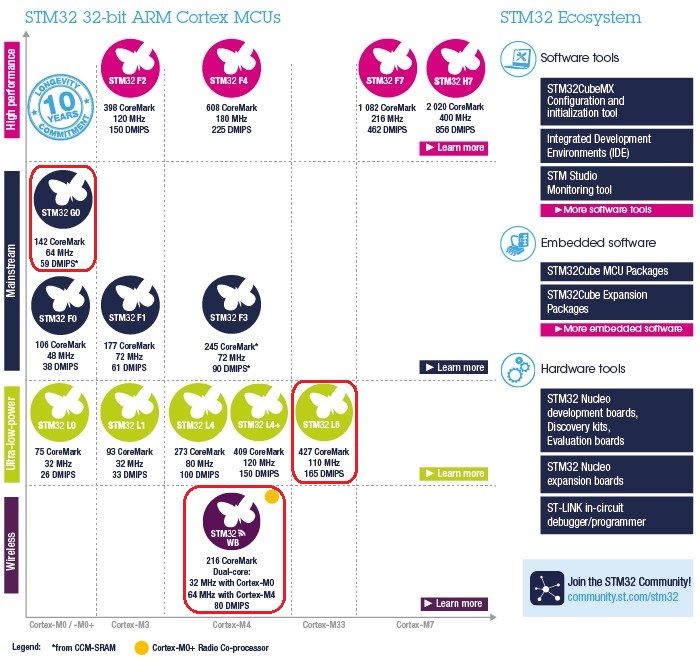

Now the image is getting larger with new products as well as ecosystem components:

Compared to the wishes you shared previous years, we weren’t able to answer all proposals for sure, but may be some of our solutions met what you looked for. Like for example: delivering .ioc file in the STM32Cube package which we started with STM32G0...

Either you are a follower of the STM32 history as well as the Community updates, or a new member in this space, would you mind share with us your feedback answering the following 3 questions:

- What shouldn’t be done (don’t say migration to new Community platform or new CubeMX interface (because both of them will be improved)?

- What you appreciate the most as STM32 related offer?

- What do you expect/suggest related to the STM32 and its ecosystem?

All together, keep UP our STM32 Community!

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-15 07:56 AM

Provide QFN with wettable flank to allow optical inspection.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-15 07:59 AM

Regarding 4): What is wrong with the uart idle interrupt?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-15 08:01 AM

Allow 1 bit SPI transfer, so that SPI can easily do JTAG and set TMS for the last SCLK.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-15 08:01 AM

Allow 1 bit SPI transfer, so that SPI can easily do JTAG and set TMS for the last SCLK.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-15 10:05 AM

About SPI: a baud rate register that allows you to configure any frequency instead of a few preset frequencies.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-15 10:18 AM

I'd be interested in knowing the staffing levels at Atollic during the last 18-24 months and whether there has been a significant loss in institutional knowledge, especially with key players moving on.

What's ST plan for Atollic, and to retain talent in 2019? There's presumably an integration/synergy play with CubeMX, GFX, etc, but still a lot of people really don't care for Eclipse/Workspaces, or the cargo-cult type button pushing approach to "writing" software.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-15 10:23 AM

I think the battle against boot-leg ST-LINK, J-LINK and U-LINK devices is pretty well lost.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-15 10:28 AM

+1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-15 01:49 PM

STM32Cube_FW_XX projects examples made using STM32CubeMx.

More Applications notes showing how to configure the peripherals at register level. Ex

...

TIM2->CCMR1 = 0x31; //ICF1 = 3 (FILTER N=8) CC1S = 01b Modo capture 1 (directed TI1-> IC1)

TIM2->CCER = 0x0A; //CC1NP =1, CC1P = 1 (both edges)

TIM2->SMCR = 0x54; //SMS = 4 (RESET), TS= 5 (trigger by TI1FP1)

...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-15 02:09 PM

For example it can't be set to an arbitrary time. There are applications where intracharacter delay may be longer than a character's time, and packets are separated by a defined much longer time. There was such requirement on this forum already.

This (and perhaps some other UART- and SPI-related requests, e.g. smart framing signal) could be better and cheaper handled by an inter-module link to timer. Similar link in the other direction could handle baudrates. This all requires thinking and real-world experience from the designers, and better documentation skills, though.

JW

- STM32 with DC current measurement capability in STM32 MCUs Products

- STM32 Trusted Package Creator NO SUPPORT FOR H743 in STM32CubeProgrammer (MCUs)

- STM32F411RE as ISO7816 Slave mode (card emulation) in STM32 MCUs Products

- How to test STM32 MCU SPI communication using Host PC ? in STM32 MCUs Products

- How to programmatically scroll up and down a scrollList in STM32 MCUs TouchGFX and GUI