- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Re: STM32 is getting stuck/frozen and enables read...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32 is getting stuck/frozen and enables read-out protection at runtime

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-30

09:18 AM

- last edited on

2023-12-01

08:15 AM

by

![]() Lina_DABASINSKA

Lina_DABASINSKA

As per our business use case, if the user removes the external supply then our device runs on a backup battery (4.4 V) for a few defined minutes and then goes into deep sleep mode. So we have defined a few wake-up events to wake the device and report the data to the cloud. This way our device runs in the long run on a backup battery.

- Labels:

-

Bug-report

-

FreeRTOS

-

STM32CubeExpansion

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-30 11:37 AM - edited 2023-11-30 11:43 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-01 05:59 AM

Thank you for your quick response and support.

At the time of our testing, we observed that there is one custom API that is accessing a flash by configuring a few flash parameters. In this custom API for various flash operations we've kept retries as well. So in the worst/failure cases there are chances of performing flash operations more than once. Can you confirm while performing these operations, the MCU can trigger the flash lock if anything goes wrong? I have attached the screenshot below for our custom API code with the highlighted portion where our suspect lies.

Thanks,

Vidhi V.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-01 06:51 AM

> Can you confirm while performing these operations, the MCU can trigger the flash lock if anything goes wrong?

Oh, actually let me walk back what I wrote, partially.

If a flash operation (non-option bytes) is interrupted, the option bytes should not be being modified. Only on option byte operations is this a possibility. So I don't think the code you posted could cause this.

That said, there are a number of threads over the years with issues like this claiming that the MCU is setting RDP=0xFF, but in my opinion none of these users actually posted very convincing evidence that the chip was to blame.

I would be interested to hear if the entire option byte section was erased, or if it was programmed with valid values (complementary values are the inverse of the real ones).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-04 06:41 AM

Hi,

I really appreciate your quick responses.

This is what I understood based on your clarification. If we perform memory operations other than the option bytes in shaky/low power, then MCU won't necessarily set the RDP. It comes into the picture only when something goes wrong during OB configuration. Please correct me if I'm wrong.

I've attached 2 screenshots where we are clearing the IWDG_STOP user OB flag. These operations are in the main function right when the MCU initialization happens. According to your clarification while performing these sequences there are chances to set RDP if anything goes wrong. Can you please confirm?

Also, the reason why we suspect on MCU chip to set the RDP rather than the code bug is that neither throughout this operation sequence nor in the whole software code did we touch OPTIONBYTE_RDP flag but instead used the OPTIONBYTE_USER flag. Do you think OPTIONBYTE_USER configuration can indirectly corrupt OPTIONBYTE_RDP?

For your knowledge, at the time of this issue, the entire option byte section was erased.

Thank you

Vidhi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-04 09:48 AM - edited 2023-12-04 09:49 AM

> If we perform memory operations other than the option bytes in shaky/low power, then MCU won't necessarily set the RDP. It comes into the picture only when something goes wrong during OB configuration.

Correct. Regular flash operations will not affect option bytes.

> According to your clarification while performing these sequences there are chances to set RDP if anything goes wrong. Can you please confirm?

Correct.

> Do you think OPTIONBYTE_USER configuration can indirectly corrupt OPTIONBYTE_RDP?

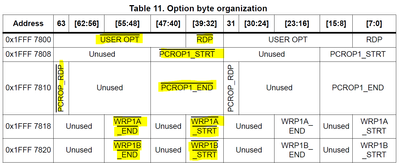

Absolutely. Whenever ANY option byte is set, the entire option byte area is erased (including RDP and whatever else is in there), then reprogrammed. At the hardware level, they cannot be modified one at a time. See the excerpt above from the reference manual.

> For your knowledge, at the time of this issue, the entire option byte section was erased.

Thanks. This lines up with what we think is happening--power loss during OB programming.

It's best to avoid writing to OB at all during production, if it can be avoided. Not sure if your particular situation, of course, but it seems reasonable to either always or never disable IWDG in stop mode.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-05 10:22 PM

Hi,

Thank you for further clarifications.

Can you please simplify this below sentence to understand what exactly you're trying to convey?

> but it seems reasonable to either always or never disable IWDG in stop mode.

Also in one of the instances, we've observed that at the time of initialization, the MCU gets stuck and then reset. On debugging, we found that a hard fault was getting triggered. Is there a chance to have HardFault triggered in case of the wrong OB configuration?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-06 06:10 AM

>Can you please simplify this below sentence to understand what exactly you're trying to convey?

>> but it seems reasonable to either always or never disable IWDG in stop mode.

Paraphrased as:

Never set option bytes during production. Choose an IWDG_STOP value and leave it alone.

> Is there a chance to have HardFault triggered in case of the wrong OB configuration?

Probably. I don't see how it could happen as a direct result, but certainly there is code logic that would result in a hard fault if OB isn't set up as expected. If the device is already bricked due to the OB being messed up, and that's the only time you saw that behavior, I wouldn't worry too much about it, although attaching a debugger and seeing the nature of the hard fault seems fast and prudent.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-06 06:38 AM

Okay. Thanks for simplifying.

I understand what you said about HardFault. Speaking of which, if the MCU gets stuck (like an infinite loop) or a hard fault occurs (Like a crash) during the execution of business logic, I assume the STM HW watchdog will be triggered and will reset the MCU. Can you please clarify if it is otherwise?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-06 07:06 AM

correct. If enabled, the watchdog will reset the chip even if it's in the hardfault handler. Of course, if it just ends up there again after reset, it doesn't help your cause much.

- Task runtime usage for ThreadX in STM32CubeIDE in STM32CubeIDE (MCUs)

- RDP level is 0xFF after power-down from programmer pins on PCB in STM32 MCUs Security

- STM32WLE5 core current consumption and NVM protection in STM32 MCUs Wireless

- STM32H563: CubeProgrammer UART connect fails in PRODUCT_STATE = iROTProvisioned in STM32 MCUs Security

- STM32H750 can not read flash bank1 while not in read protection in STM32 MCUs Products