- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Re: Minimizing SCLK pulse time on SPI with STM32H7...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Minimizing SCLK pulse time on SPI with STM32H745

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-22 06:37 AM

Hello STM community,

I'm working on optimizing SPI communication on an STM device, and I'm encountering an issue with the timing of SCLK pulses. After transmitting 16 SCLK pulses, there's a delay of 3μs before the next set of 16 pulses can be generated.

I need to reduce this delay to ensure that SCLK can be immediately generated after CS goes low. Can anyone suggest methods or configurations to minimize this delay and maintain a continuous SCLK stream after CS is pulled low?

I'm trying to achieve sampling rate for ADC ADS7046 interfacing.

sclk take same time even not used CS.

I want to sclk immediately on after cs low.

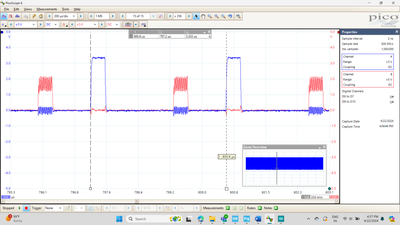

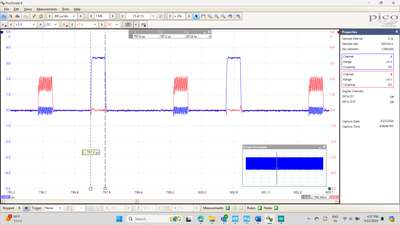

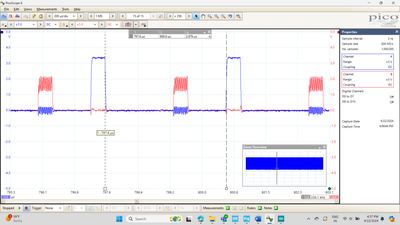

Below I attach some snap of spi cycle.

- Labels:

-

STM32Cube MCU Packages

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-22 06:40 AM

Use DMA.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-22 06:44 AM

Start by using the FIFO.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-22 06:48 AM

If you need the framing with CS, read the reference and understand how NSS can be used to automaitcally generate the frame around a packet.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-22 09:50 PM - edited 2024-04-22 09:51 PM

Hello Uwe Bonnes,

Thanks for reply. I also used DMA with normal mode then frame also same as above with additional delay. So then I am trying with circular DMA that time data not read as given. and SCLK generated continuous and cs not toggle. please can you provide one example code with stm32h745 SPI DMA. I want to achieve 3msps sampling rate for ADC ads7046.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-23 01:36 AM

The timing above does not look like hardware NSS. When using hardware NSS the timing between NSS and clock and between transfers is set by SPI_CFG2_MIDI and MSSI. HAL will probably have a way to set hardware NSS and those values, adding however a level of obfuscation between the reference manual and theseetings needed by HAL

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-23 02:39 AM - edited 2024-04-23 02:40 AM

yes Uwe Bonnes, can you please provide example code and setting what to do. and which mode i need to select normal or circular dma?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-23 02:44 AM

I do not use HAL

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-23 03:30 AM

it's ok. can you share it. any type of example you can share.

now i used with hardware nss

blue= sclk, red= nss

how can i minimize sclk time

without buffer print it also take same time.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-04-23 03:38 AM

- Minimizing SCLK pulse time on SPI with STM32H745 in STM32 MCUs Embedded software

- STM32h timers in STM32 MCUs Products

- HAL_TIM_IC_Start_DMA() with dma I am not getting the raising or falling edge ? in STM32 MCUs Products

- What is the minimal required injected current for the one-pulse mode is it the same that for an GPIO input ? in STM32 MCUs Products

- How I can capture the raising edge or falling edge in the STM32H745-nucleo timer? in STM32 MCUs Products