- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- FatFs/SDMMC with 4 wires times out, 1 wire works

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FatFs/SDMMC with 4 wires times out, 1 wire works

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-10 04:54 AM

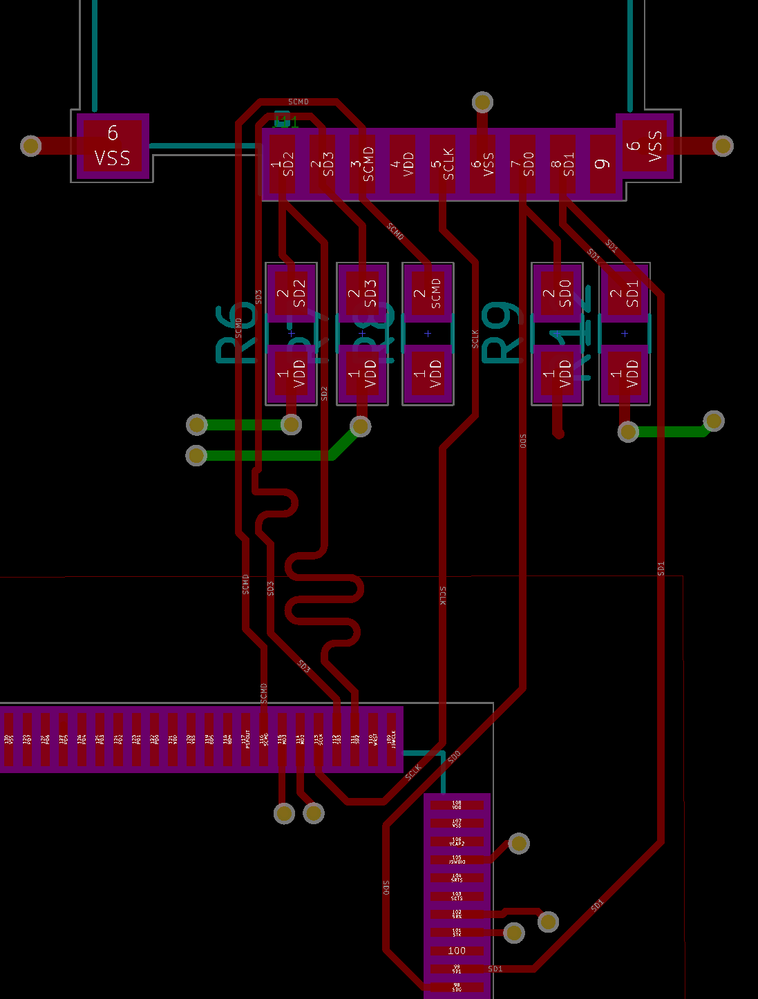

I'm still trying to get FatFs to work with 4 wires. My PCB has been properly traced, each line is within a few mm of all others, and has a 33K pull-up. Internal pull-ups are off.

This setup works fine at full-speed (45 MHz) when using only 1 wire, but when I select all 4 wires in CubeMX, the code hangs in stm32f7xx_hal_sd.c, in the /* Poll on SDMMC flags */ loop. It probably should time out, but doesn't. This doesn't change if I lower the speed to 3 MHz.

My concern is not the timeout, though, but why 4 wires are still not working. Could someone advise on my PCB if everything is alright there? Are the pull-ups placed OK? The SD1 trace accidentally hit the resistor pad, but is this already enough to mess everything up?

- Labels:

-

FatFS

-

SDIO-SDMMC

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-10 06:26 AM

With better routing you could have entirely lost those stub traces to the resistors.

On the settings you can try turn off the pull-up at the STM32 pin, and also reduce the slew-rate (speed) that you're driving into relatively short traces. The GPIO_SPEED_FREQ_VERY_HIGH setting is likely to cause ringing/overshoot.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-10 09:28 AM

Thanks, I've decreased the speed to "high" now. Alas, this didn't solve the problem.

What kind of routing would you recommend? Like the one I used for SD3? Since the upper half is blocked by the uSD connector, I placed the pull-ups below. I realized later that these are no caps, and can be placed further away, up to the side of the uSD connector.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-10 11:37 AM

>>What kind of routing would you recommend?

Feed thru on the the pad, ie in one side, out the other, rather the out and back excursion.

Not entirely sure this is a routing issue, I can push much higher frequencies down 3" leads.

Clocking the SDMMC peripheral at 45 MHz, or SCLK at 45 MHz via ClockDiv?

Presuming PC8..12 for D0..D3,CLK and PD2 CMD

What is your HSE source? What USART pins for debugging?

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-10 11:52 AM

Got it, thanks!

I'm using HSI, HCLK is 190 MHz, and SDMMC1 is 47.5 MHz. I currently bypass the extra SDMMCCLK divider, but tested down to /32.

Pins are correct, logging is UART6, only RX/TX. Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-10 01:32 PM

>> UART6, only RX/TX.

Which pins?

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-10 06:48 PM

Quick test with PC6/PC7, outputs at 115200 8N1

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-11 10:53 AM

Thanks for the file, Clive. I wanted to give it a quick try right now, but for some reason my upload via UART doesn't work any more on my new board. I'll try in earnest on the weekend.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-12 02:52 AM

Sorry for the delay, here's the result of your test program:

Nucleo F722ZE

Core=190000000, 190 MHz

CPUID 411FC271 DEVID 452 REVID 1000

Cortex M7 r1p1

STM32F72xxx or F73xxx

C0000000 FFFFFFF8 00000000

10110021 11000011 00000040

FPU-S Single-precision only

HCLK=190000000

APB1= 47500000

APB2= 95000000

BSP_SD_Init - SDMMC Build

Switching to 4-bit mode

FatFs Testing (68300)

SystemCoreClock: 190000000

Mounting FatFs

BSP_SD_Init - SDMMC Build

Switching to 4-bit mode

R 0 1 20000160 FAIL (00000000)

res = 1 f_getfree

Infinite loop...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-12 07:58 AM

I'm so sorry Clive. I just resoldered the uSD connector, and now everything is working fine. I should've thought of that earlier, but the connections looked fine.

Anyway, you'll have mail.

- STM327H73 and USB2514 continued problems in STM32 MCUs Embedded software

- STM32U575 DMA2D - Synchronize framebuffer access in STM32 MCUs TouchGFX and GUI

- Encoder on STM32U083 gives interrupts too late while counting up in STM32 MCUs Boards and hardware tools

- STM32H5 high cycle flash read. in STM32 MCUs Products

- NUCLEO-C071RB Interrupt problem in STM32CubeMX (MCUs)