- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Bug report STM32CubeMX 4.25.0 - Activating ''Audio...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Bug report STM32CubeMX 4.25.0 - Activating ''Audio Clock Input'' (I2S_CKIN) does not set I2SSRC bit in RCC_CFGR register

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-29 11:08 PM

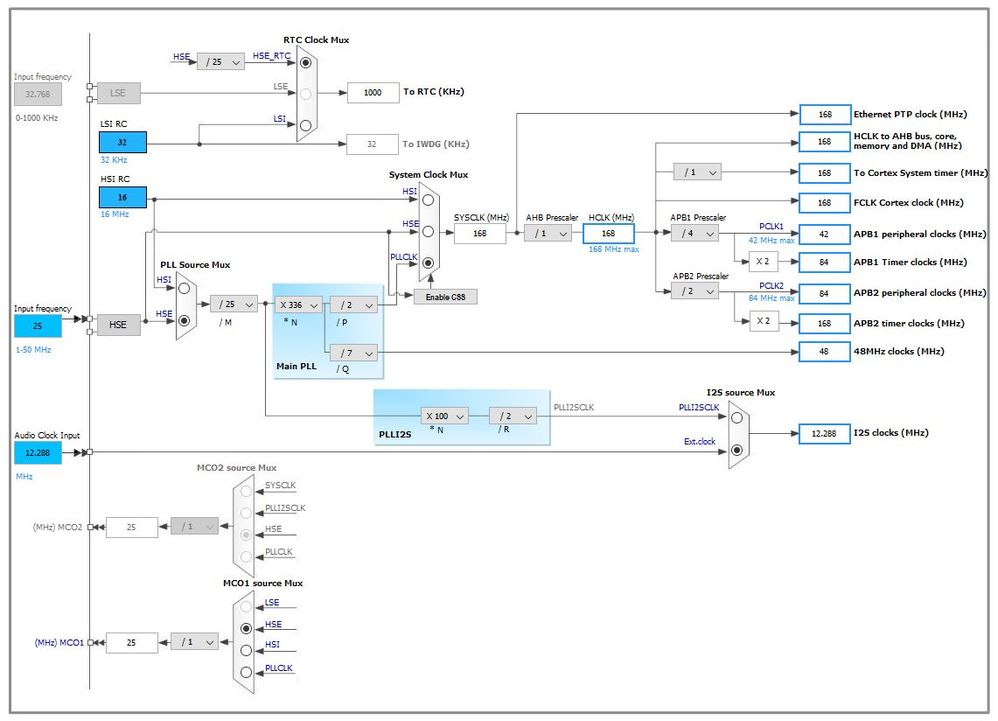

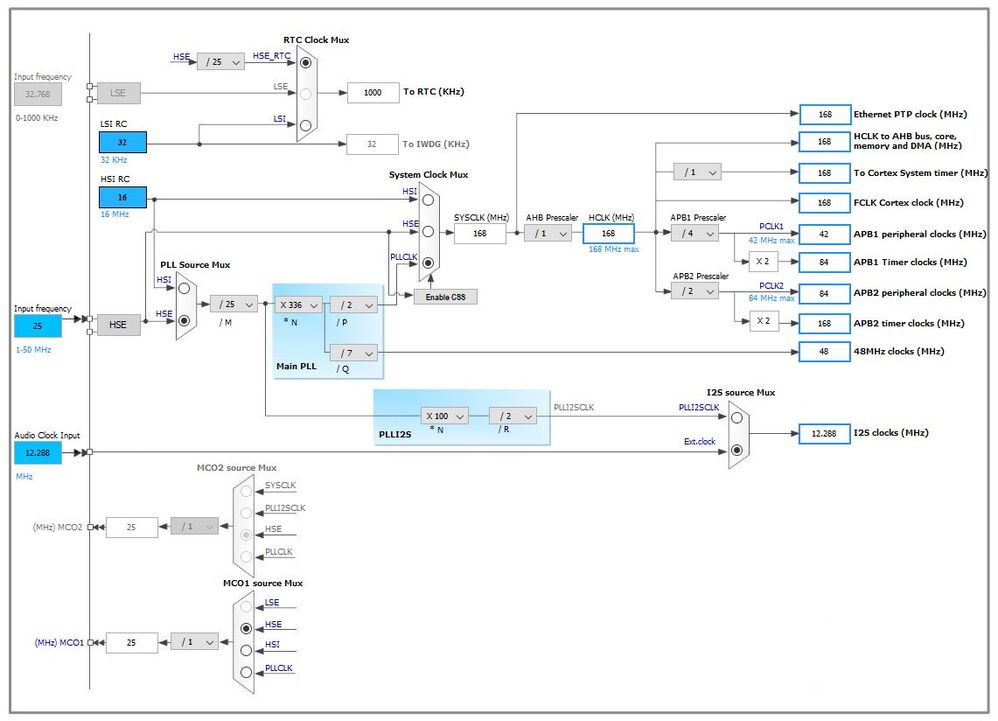

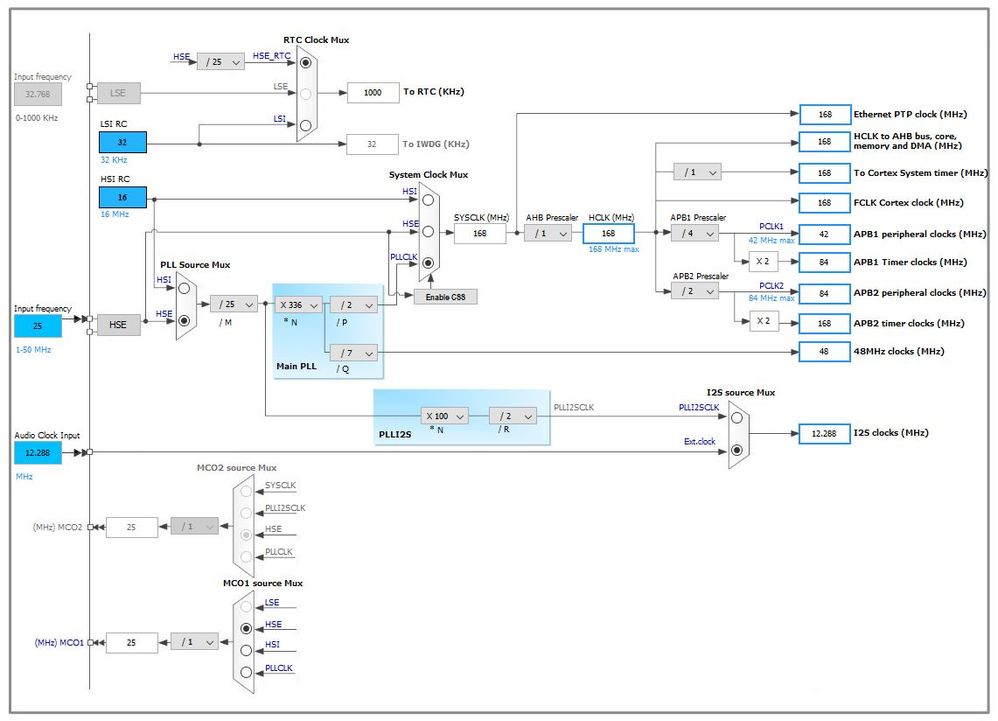

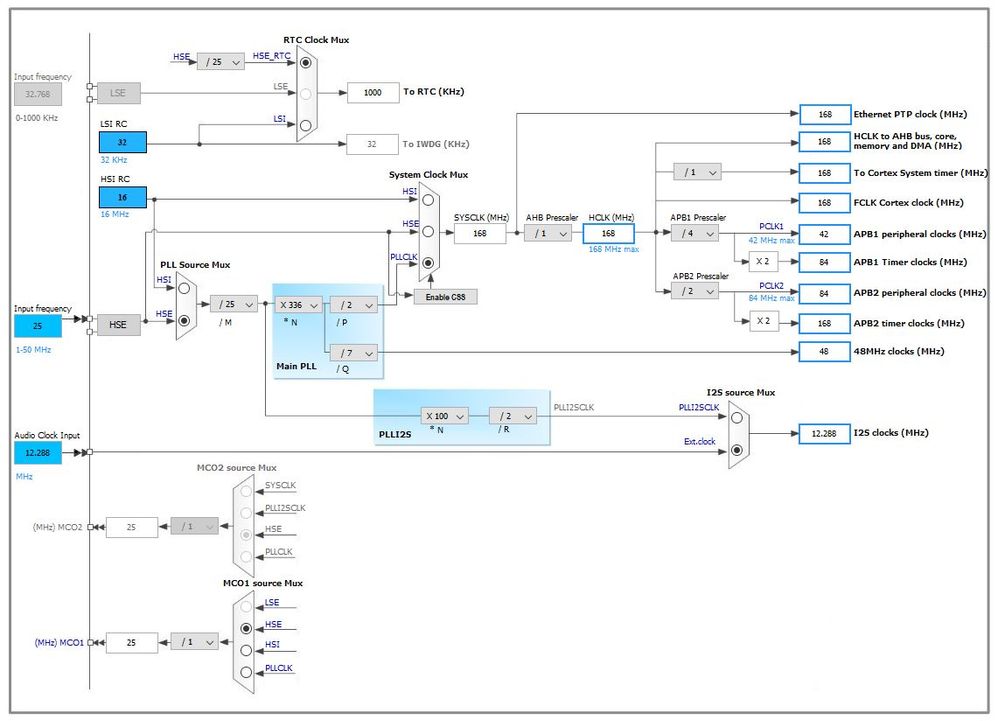

I have a project generated by &sharpSTM32CubeMX 4.25.0 using firmware STM32Cube FW_F4 V1.21.0. The clock configuration can be found in the attached picture below. When I debugged the generated code I have seen that I2SSRC bit in RCC_CFGR register was not set to 1; which causes I2S malfunctioning.

/* I2S3 init function */

void MX_I2S3_Init(void){hi2s3.Instance = SPI3;

hi2s3.Init.Mode = I2S_MODE_MASTER_TX; hi2s3.Init.Standard = I2S_STANDARD_PHILIPS; hi2s3.Init.DataFormat = I2S_DATAFORMAT_16B; hi2s3.Init.MCLKOutput = I2S_MCLKOUTPUT_DISABLE; hi2s3.Init.AudioFreq = I2S_AUDIOFREQ_8K; hi2s3.Init.CPOL = I2S_CPOL_LOW; hi2s3.Init.ClockSource = I2S_CLOCK_EXTERNAL; hi2s3.Init.FullDuplexMode = I2S_FULLDUPLEXMODE_ENABLE; if (HAL_I2S_Init(&hi2s3) != HAL_OK) { _Error_Handler(__FILE__, __LINE__); }}

void HAL_I2S_MspInit(I2S_HandleTypeDef* i2sHandle)

{GPIO_InitTypeDef GPIO_InitStruct;

if(i2sHandle->Instance==SPI3) { /* USER CODE BEGIN SPI3_MspInit 0 *//* USER CODE END SPI3_MspInit 0 */

/* I2S3 clock enable */ __HAL_RCC_SPI3_CLK_ENABLE(); /**I2S3 GPIO Configuration PA4 ------> I2S3_WS PC10 ------> I2S3_CK PC11 ------> I2S3_ext_SD PC12 ------> I2S3_SD */ GPIO_InitStruct.Pin = GPIO_PIN_4; GPIO_InitStruct.Mode = GPIO_MODE_AF_PP; GPIO_InitStruct.Pull = GPIO_NOPULL; GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_MEDIUM; GPIO_InitStruct.Alternate = GPIO_AF6_SPI3; HAL_GPIO_Init(GPIOA, &GPIO_InitStruct);GPIO_InitStruct.Pin = GPIO_PIN_10|GPIO_PIN_12;

GPIO_InitStruct.Mode = GPIO_MODE_AF_PP; GPIO_InitStruct.Pull = GPIO_NOPULL; GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_MEDIUM; GPIO_InitStruct.Alternate = GPIO_AF6_SPI3; HAL_GPIO_Init(GPIOC, &GPIO_InitStruct);GPIO_InitStruct.Pin = GPIO_PIN_11;

GPIO_InitStruct.Mode = GPIO_MODE_AF_PP; GPIO_InitStruct.Pull = GPIO_NOPULL; GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_MEDIUM; GPIO_InitStruct.Alternate = GPIO_AF5_I2S3ext; HAL_GPIO_Init(GPIOC, &GPIO_InitStruct);/* I2S3 DMA Init */

/* I2S3_EXT_RX Init */ hdma_i2s3_ext_rx.Instance = DMA1_Stream0; hdma_i2s3_ext_rx.Init.Channel = DMA_CHANNEL_3; hdma_i2s3_ext_rx.Init.Direction = DMA_PERIPH_TO_MEMORY; hdma_i2s3_ext_rx.Init.PeriphInc = DMA_PINC_DISABLE; hdma_i2s3_ext_rx.Init.MemInc = DMA_MINC_ENABLE; hdma_i2s3_ext_rx.Init.PeriphDataAlignment = DMA_PDATAALIGN_WORD; hdma_i2s3_ext_rx.Init.MemDataAlignment = DMA_MDATAALIGN_WORD; hdma_i2s3_ext_rx.Init.Mode = DMA_CIRCULAR; hdma_i2s3_ext_rx.Init.Priority = DMA_PRIORITY_HIGH; hdma_i2s3_ext_rx.Init.FIFOMode = DMA_FIFOMODE_ENABLE; hdma_i2s3_ext_rx.Init.FIFOThreshold = DMA_FIFO_THRESHOLD_FULL; hdma_i2s3_ext_rx.Init.MemBurst = DMA_MBURST_SINGLE; hdma_i2s3_ext_rx.Init.PeriphBurst = DMA_PBURST_SINGLE; if (HAL_DMA_Init(&hdma_i2s3_ext_rx) != HAL_OK) { _Error_Handler(__FILE__, __LINE__); }__HAL_LINKDMA(i2sHandle,hdmarx,hdma_i2s3_ext_rx);

/* SPI3_TX Init */

hdma_spi3_tx.Instance = DMA1_Stream5; hdma_spi3_tx.Init.Channel = DMA_CHANNEL_0; hdma_spi3_tx.Init.Direction = DMA_MEMORY_TO_PERIPH; hdma_spi3_tx.Init.PeriphInc = DMA_PINC_DISABLE; hdma_spi3_tx.Init.MemInc = DMA_MINC_ENABLE; hdma_spi3_tx.Init.PeriphDataAlignment = DMA_PDATAALIGN_WORD; hdma_spi3_tx.Init.MemDataAlignment = DMA_MDATAALIGN_WORD; hdma_spi3_tx.Init.Mode = DMA_CIRCULAR; hdma_spi3_tx.Init.Priority = DMA_PRIORITY_HIGH; hdma_spi3_tx.Init.FIFOMode = DMA_FIFOMODE_ENABLE; hdma_spi3_tx.Init.FIFOThreshold = DMA_FIFO_THRESHOLD_FULL; hdma_spi3_tx.Init.MemBurst = DMA_MBURST_SINGLE; hdma_spi3_tx.Init.PeriphBurst = DMA_PBURST_SINGLE; if (HAL_DMA_Init(&hdma_spi3_tx) != HAL_OK) { _Error_Handler(__FILE__, __LINE__); }__HAL_LINKDMA(i2sHandle,hdmatx,hdma_spi3_tx);

/* USER CODE BEGIN SPI3_MspInit 1 */

/* USER CODE END SPI3_MspInit 1 */

}}#stm32cubemx-4.25.0 #i2ssrc #stm32f4 #rcc_cfgr #audio-clock-input- Labels:

-

Audio

-

I2S

-

RCC

-

STM32CubeMX

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-03 8:12 AM

Hi

metecantimur

,Could you please precise on which device you have found the issue. So, we can verify it.

Best Regards,

Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-04 1:32 AM

Hi

DAHMEN.IMEN

,I am using STM32F407ZGTx MCU device in an proprietary board.

Best Regards,

Mete

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-04 7:44 AM

Hi

DAHMEN.IMEN

,I have the following workaround steps for the problem:

1) Insert the following line into the function

HAL_I2S_MspInitjust before the line containing __HAL_RCC_SPI3_CLK_ENABLE();

/* BUG FIX: Enabling Audio Clock Input in CubeMX does not set I2SSRC bit

* in RCC_CFGR register! Hence we need to set it manually here! * WARNING: A bug fix is also needed in __HAL_RCC_GET_I2S_SOURCE() */

__HAL_RCC_I2S_CONFIG(RCC_I2SCLKSOURCE_EXT);

2) Apply the following patch to the following macro in library the file 'stm32f4xx_hal_rcc_ex.h' at line 6112:

#define __HAL_RCC_GET_I2S_SOURCE() ((uint32_t)(READ_BIT(RCC->CFGR, RCC_CFGR_I2SSRC)) >> RCC_CFGR_I2SSRC_Pos) /*BUG FIX: MC*/

Note: I will report the bug in filestm32f4xx_hal_rcc_ex.h

at line 6112 as a new bug report.

Best Regards,

Mete

- STM32G0B1 USB HID Host in STM32CubeIDE (MCUs)

- Build Error in STM32H747-DISCO Project with TouchGFX, CubeMX, and FreeRTOS in STM32CubeMX (MCUs)

- Why DSI clock can't set to more than 500M in STM32H747? in STM32 MCUs Products

- GPIO Stops Toggling When Timer and SPI DMA Are Active on NUCLEO-H753ZI in STM32 MCUs Embedded software

- MX cube corrupts .ioc on save (Windows 11) in STM32CubeMX (MCUs)