- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Boards and hardware tools

- Re: STM32H743 has QSPI_IOs not in High Impedance M...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H743 has QSPI_IOs not in High Impedance Mode when Configured as Input

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 7:13 AM

Solved! Go to Solution.

- Labels:

-

ST boards

-

STM32H7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 3:16 PM

I think the QUADSPI just doesn't behave how you want it to. It's really misnamed, it's not just SPI but with 4 lines, it's really a specialized interface for QSPI flash.

Per the reference manual, if you're not actively sending clocks, all IO pins will be in output mode.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 8:41 AM

Is the pin in AF mode (for QUADSPI), or input mode? Can you show the pin initialization?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 9:35 AM

Something seems seriously wrong or damaged. Perhaps you have a schematic so we can understand what you've fashioned?

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 9:58 AM

The Pins are configured as Alternate Function Push-Pull for QUADSPI.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 10:00 AM

The behaviour occurs on a bare Nucleo-H743 board and also on a bare Nucleo-F767 board, all I do is configuring the QUADSPI with nothing connected and then short the pin which should be configured as an input to 3V3 with a multimeter.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 3:16 PM

I think the QUADSPI just doesn't behave how you want it to. It's really misnamed, it's not just SPI but with 4 lines, it's really a specialized interface for QSPI flash.

Per the reference manual, if you're not actively sending clocks, all IO pins will be in output mode.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-15 7:11 AM

I agree with the first part, and probably can't (ab)use QuadSPI in the way I want to.

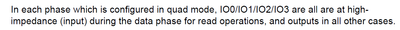

For the RM part (page 884, section 23.3.4, in RM0433 Rev 8 for all future readers), I did not read that part the way you do. The wording doesn't explicitly state what exactly constitutes "all other cases", because I read it as "all other phase cases". This would also include Dummy Cycles, but I think the pins switch to input already during dummy cycles. But your reading certainly matches the behaviour I observe, so thanks for the hint!

- H7 USB devices Errata in STM32 MCUs Embedded software

- CubeMx MAJOR BUG in UsbX configuration.... in STM32CubeMX (MCUs)

- How to correctly dimension an external pullup resistor in Low Power application in STM32 MCUs Wireless

- The GPIO output before initialization in STM32 MCUs Products

- STM32H743 HCLK3 frequency error in Clock Configuration for HPRE=1 in STM32CubeMX (MCUs)