- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Boards and hardware tools

- Re: Decoupling capacitor placement

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Decoupling capacitor placement

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-16 01:09 AM

Hi,

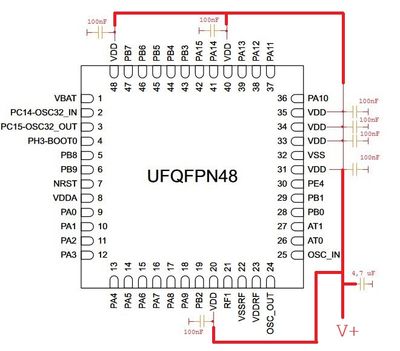

I am currently optimizing some designs and started thinking about decoupling capacitors. As far as I know, it is a rule of thumb to place "one 100 nF capacitor per V+ pin".

In the attached document, ST recommends exactly this. Let´s look at the document: n x 100 nF + 1 x 4,7 uF. I interpret this in the following way: For each VDD pin, I have to place one 100 nF capacitor (as close as possible to the pin) and, overall, I need an additional 4,7 uF capacitor.

Now two questions arise:

-If you look at pins 33, 34 and 35, do I really need three single 100 nF capacitors? Couldn´t I just place one 300 nF in the middle? Or maybe one 100 nF would also suffice?

-Where do I place the 4,7 uF capacitor? The pins are quite far apart. Do I just place it "somewhere"?

I think I understand the theory that the capacitors serve as an energy buffer when the uC has transient changes in current draw and that they filter out high frequency spikes on the traces.

I have a two layer PCB and I am looking for a practical answer for this particular case.

Kind regards

René

- Labels:

-

Schematic

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-16 03:44 AM - edited 2023-09-16 03:48 AM

100n is old rule of thumb, not more. and still working most times.

if you want understand, you need to think yourself...

what we want / is needed ? we want a broadband low impedance supply for a chip. ok?

so we connect to all gnd and vcc pins a wire and other end to supply input, or onboard regulator.

problem : physics...every wire/lane has resistance and inductance . ok?

Assumed, wires/traces are thick enough, forget resistance. but inductance stays almost same. ok?

digital chip will use current in form of short spikes, creating a lot of resonances and cannot work. ok?

there are two possible solutions :

1. (look at a "standard" PC mainboard : many fast chips there, 100MHz up to 6Ghz, and no 100nF caps on all power pins..(would need hundreds of them), just some big low esr caps strayed all over the board). why?

they use 6..10 layer board, gnd and vcc full planes close together. this is a: a distributed capacitance all over the bord, and same time a waveguide with low impedance (maybe 2 ohm or less), effective from low frequencies up to many GHz; here put some low impedance caps distributed over the board and you get low impedance on all chip/pins that contact direct (via) to the supply layers.

clever, eh ?

but if we dont have a big 10 layer board , only 2 layer ?

2. we use a ground layer, but to vcc pins we need wires - with inductance. ok?

to reduce ringing, we put as close as possible, mlcc cer. caps close to all vcc pins (and to gnd layer).

no the remaining problem: every of these caps forms a resonance peak with the inductance of the line . ok?

so using many different sized caps (as often recommended) forms many resonance peaks and dips, what we dont want. ok?

to really do it perfect, you need to do a simulation, with all caps and wires (every 1mm gives about 1 nH ) , to see what will happen. and dont forget the 5..15 mm from pin to chip contact, depending on case of cpu/chip.

if simulation is too much effort, just use only one size of cap and put 100n or 1u mlcc close to every vcc pin and all lines together, to supply input.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-16 04:22 AM

-If you look at pins 33, 34 and 35, do I really need three single 100 nF capacitors? Couldn´t I just place one 300 nF in the middle? Or maybe one 100 nF would also suffice?

- The Capacitor has a resistor inside so this is a difference for 3x100nF and one 300nF because one 300nF is a single resistor series to capacitor and 3x100nF are 3 resistor parallel which it is lower than single one.

-Where do I place the 4,7 uF capacitor? The pins are quite far apart. Do I just place it "somewhere"?

- on somewhere has more pin connected to it because it usually has more space and lowest resistance between capacitor and controller.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-16 05:40 AM

- if enough room, place 3 x 100n . or 1x 100n, if no space.

- the 4.7u where you bring all vcc lines together

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-16 06:45 AM - edited 2023-09-16 08:41 AM

<do I really need three single 100 nF capacitors? Couldn´t I just place one 300 nF in the middle?>

Edit: At high frequencies a 300 nF capacitor does not provide equal performance to 3 x 100 nF capacitors. The larger the capacitor, the lower the high frequency performance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-16 11:13 PM

Ok, so to summarize:

As I don´t have the software for a simulation, I will stick to the recommendation and use 1 nF capacitor per VDD pin, even if that means that I have three capacitors in close proximity to each other. The board space is sufficient for that placement.

The 4,7 uF capacitor will be placed either where I tie the VDD lines together or in the area where there is most "demand".

like this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-16 11:52 PM

that can be like that but if it's possible that the power line should not be like a L or C or U shape because that 's going to generate some magnetic field and it can induce the other track.

and the controller should not place in middle of power line path, it 's should be end point of power line to reduce current pass through them.

there are some considering on design.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-17 11:18 PM

Ok, thank you all for the helpful advice!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-18 12:20 AM

+++ dont forget to connect all VDDA + AGND pins to vcc + gnd .

- TSC: STM32U031R8T6 LEDs "near" Touch Sensors in STM32 MCUs Boards and hardware tools

- Usage of decoupling capacitor in STM32H503KBU6 in STM32 MCUs Products

- High current draw Vbat Bluepill in STM32 MCUs Products

- STM32G431C6 fails to power up sometimes. in STM32 MCUs Products

- STM32F4 RTC ISSUE WHEN COINCELL [VBAT] IS REMOVED in STM32 MCUs Products