- STMicroelectronics Community

- Product forums

- Power management

- stepper motor ramp profile using timer 1 output co...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

stepper motor ramp profile using timer 1 output compare

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-08-28 06:19 PM

timer 1 output compare to generate Step output for stepper motor

I am using timer1 channel 1 as output compare, to generate a pulse of variable period.

Desire output – In the beginning the output remain low for 4 ms(delay period) and then pulses of variable periods as 5.8, 3.6, 2.7,2.3, …. The desired time periods are stored in RAM. (Frequency range 170 Hz to 1.5 KHz)

The timer clock is configured to 1 MHz frequency. The output mode is set to toggle mode and the polarity is set to active high. The capture compare interrupt is enabled.

And the capture compare register is set to delay period and then in next interrupt, the capture compare register set to first period and next period will be updated after the one pulse is completed.The problem facing is that the beginning delay period is variable and sometimes missing.

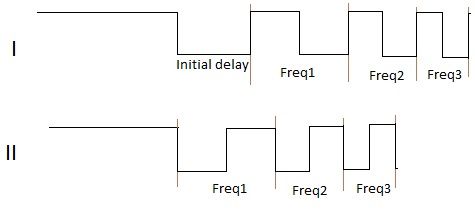

If initial delay is not missing then the following output periods are correct as expected. If the low period is missing then the first period start from low rather than high which results in wrong steps

I is the correct expected output, II is wrong one.

why timer output compare not working properly ?? why it miss the first delay ??

- Labels:

-

Motor Control Hardware

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-09-22 12:25 AM

Hi, I suggest you to move this question in the forum dedicated to the motor control firmware.

This section is focused on the integaretd motor driving devices. Kind Regards Enrico- STM32F030T8C6 PWM Not Setting new PWM Value. in STM32 MCUs Products

- STM32 PWM Output Incorrect Frequency (PE9, TIM1) despite Correct Configuration in STM32 MCUs Embedded software

- DMA and OC MODE in STM32 MCUs Motor control

- STM32CubeIDE - SWV Profiling in STM32CubeIDE (MCUs)

- Server error 61234 due to timer configuration on NUCLEO F401RE and STM32F103C8TX in STM32 MCUs Motor control