- STMicroelectronics Community

- MEMS and sensors

- MEMS (sensors)

- Re: about interrupt1 of lsm6dso

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

about interrupt1 of lsm6dso

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-15 03:39 AM

Lsm6dso is configered as mode1; ODR is 26hz or 52hz ,INT1 is configured as threshold interrupt;

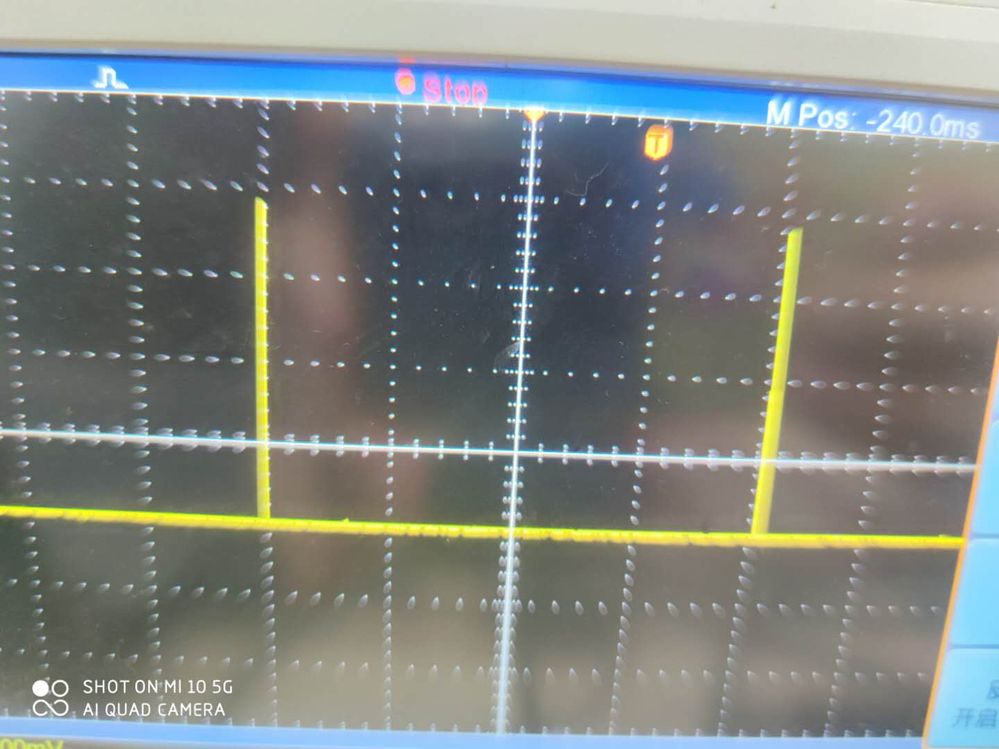

Problem: interrupt interval should be 1s, but measured time is larger than 1s such as 1016ms. We measured 3 boards and 2 of them exist this problem. How can we deel with it?

- Labels:

-

Developers Corner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-16 02:46 AM

Hi @Dw.1 , it could be an issue related to the fact that the interrupt duration resolution is typically defined with a resolution of t=1/ODR, meaning 38ms at 26Hz and 19ms at 52Hz... which is the threshold event that you are detecting, FIFO threshold? Can you please check if you get the same misalignment increasing the output ODR? Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-17 12:06 AM

I test these ODR(26Hz, 52Hz, 104Hz, 208Hz) with one board, and get the same misalignment (16ms) ;

What should I do next?

Best Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-17 12:11 AM

Which kind of threshold interrupt are you using? I mean, which is the external event that should trigger your LSM6DSO every 1 second? Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-17 02:09 AM

Threshold interrupt is used for collecting 6D orientation data;

the code is as follows:

lsm6dso_device_id_get(&m_dev_ctx, &chip_id);

if (chip_id != LSM6DSO_ID)

{

LOG_ERROR("lsm6dso read register chip id error(%X)", chip_id);

return NRF_ERROR_INVALID_STATE;

}

/* Restore default configuration */

lsm6dso_reset_set(&m_dev_ctx, PROPERTY_ENABLE);

do

{

lsm6dso_reset_get(&m_dev_ctx, &rst);

} while (rst);

/* Disable I3C interface */

lsm6dso_i3c_disable_set(&m_dev_ctx, LSM6DSO_I3C_DISABLE);

/* Enable Block Data Update */

lsm6dso_block_data_update_set(&m_dev_ctx, PROPERTY_ENABLE);

/* Set full scale */

lsm6dso_xl_full_scale_set(&m_dev_ctx, LSM6DSO_2g);

// lsm6dso_gy_full_scale_set(&m_dev_ctx, LSM6DSO_2000dps);

/* Set FIFO watermark (number of unread sensor data TAG + 6 bytes

* stored in FIFO) to 10 samples

*/

lsm6dso_fifo_watermark_set(&m_dev_ctx, LSM6DSO_MAX_DATA_SIZES);

/* Set FIFO batch XL/Gyro ODR to 26Hz */

lsm6dso_fifo_xl_batch_set(&m_dev_ctx, LSM6DSO_XL_BATCHED_AT_26Hz);

lsm6dso_fifo_gy_batch_set(&m_dev_ctx, LSM6DSO_GY_NOT_BATCHED);

/* Set FIFO mode to Stream mode (aka Continuous Mode) */

lsm6dso_fifo_mode_set(&m_dev_ctx, LSM6DSO_STREAM_MODE);

/* Enable drdy 75 μs pulse: uncomment if interrupt must be pulsed */

lsm6dso_data_ready_mode_set(&m_dev_ctx, LSM6DSO_DRDY_PULSED);

/* Uncomment if interrupt generation on Free Fall INT1 pin */

lsm6dso_pin_int1_route_get(&m_dev_ctx, &int1_route);

// int1_route.reg.int1_ctrl.int1_fifo_th = PROPERTY_ENABLE;

int1_route.fifo_th = PROPERTY_ENABLE;

lsm6dso_pin_int1_route_set(&m_dev_ctx, int1_route);

/* Set Output Data Rate */

lsm6dso_xl_data_rate_set(&m_dev_ctx, LSM6DSO_XL_ODR_26Hz);

lsm6dso_gy_data_rate_set(&m_dev_ctx, LSM6DSO_GY_ODR_OFF);

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-20 06:29 AM

Hi @Dw.1 , it doesn't seem you configured the 6D axis interrupt in your code above... The settings of the 6D interrupt is described in the app note AN5192 at p. 44 and the procedure is described in the following sequence:

1. Write 60h to CTRL1_XL // Turn on the accelerometer

// ODR_XL = 417 Hz, FS_XL = ±2 g

2. Write 41h to TAP_CFG0 // Enable latch mode with reset on read

3. Write 80h to TAP_CFG2 // Enable interrupt function

4. Write 40h to TAP_THS_6D // Set 6D threshold (SIXD_THS[1:0] = 10b = 60 degrees)

5. Write 01h to CTRL8_XL // Enable LPF2 filter to 6D functionality

6. Write 04h to MD1_CFG // 6D interrupt driven to INT1 pinFor example, I cannot see in which part of your code you configured these registers ...

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-09-03 02:47 AM

The cycle of interrupt1 is not 1s but 1.016s.

The code is as follows:

uint8_t reg_data;

reg_data = 0;

lsm6dso_ic_write_register(NULL, LSM6DSO_WAKE_UP_DUR, ®_data, 1);

reg_data = 2;

lsm6dso_ic_write_register(NULL, LSM6DSO_WAKE_UP_THS, ®_data, 1);

reg_data = 0x51;

lsm6dso_ic_write_register(NULL, LSM6DSO_TAP_CFG0, ®_data, 1);

reg_data = 0x80;

lsm6dso_ic_write_register(NULL, LSM6DSO_TAP_CFG2, ®_data, 1);

reg_data = 0x70;

lsm6dso_ic_write_register(NULL, LSM6DSO_CTRL1_XL, ®_data, 1);

nrf_delay_ms(4);

reg_data = 0x10;

lsm6dso_ic_write_register(NULL, LSM6DSO_CTRL1_XL, ®_data, 1);

reg_data = 0x20;

lsm6dso_ic_write_register(NULL, LSM6DSO_MD1_CFG, ®_data, 1);

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-09-14 05:45 AM

Hi @Dw.1 ,

let me please check internally and get back to you asap.

-Eleon