- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Hello i was reading the "STM32 microcontroller sys...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

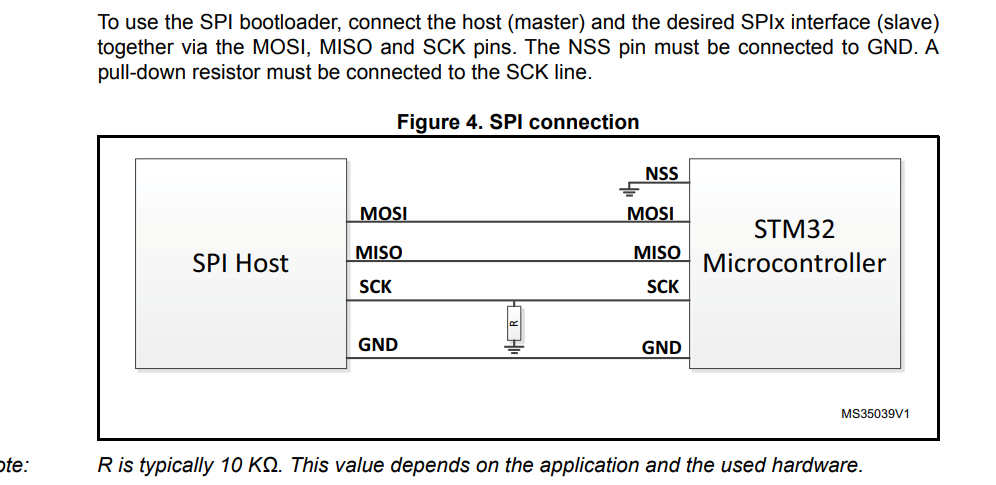

Hello i was reading the "STM32 microcontroller system memory boot mode" documantation and I saw SPI SCK pin pulled down via 10Kohm resistor in SPI connection part. I couldn't see any reason for that. Why SCK pin needs pul down?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-01-25 07:01 AM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-01-25 12:21 PM

Welcome, @EKOSE.1, to the community!

You are referring to AN2606, section 4.3, Hardware connection requirements, right?

In order not to interpret interspersed interference pulses as an apparent clock pulse to SCK during periods where SCK is floating, the connection line should be pulled low.

Does it answer your question?

Regards

/Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-01-25 12:21 PM

Welcome, @EKOSE.1, to the community!

You are referring to AN2606, section 4.3, Hardware connection requirements, right?

In order not to interpret interspersed interference pulses as an apparent clock pulse to SCK during periods where SCK is floating, the connection line should be pulled low.

Does it answer your question?

Regards

/Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-01-25 12:45 PM

Yes i reffered the AN2606. Thanks for your answer. You explained well.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-01-25 01:18 PM

Great!

If the problem is solved, please mark this thread as answered by selecting Select as best, as also explained here. This will help other users find that answer faster.

Regards

/Peter

- How to check Stop mode current consumption on Nucleo-L073 board in STM32 MCUs Embedded software

- Target no device found & Can not connect to target! and No STM32 target found! in STM32 MCUs Boards and hardware tools

- USB DFU doesn't properly erase application flash, only allowing me to program once in STM32 MCUs Products

- [STM32G431] Programming issue in STM32 MCUs Products

- Configuration of an HID (standard Joystick) via PC-Software in STM32 MCUs Embedded software