- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32G030 DMA to GPIO BSRR bus error

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32G030 DMA to GPIO BSRR bus error

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-04 2:31 AM

Hi

STM32G0 series is a newer chip family with more advanced DMA/MUX to provide more flexibility.

my code, which uses tim16 update to request DMA to transfer from memory to GPIO BSRR. The code works on STM32F030 but fail in G030. The request from TIM16 gets through DMA, and it is the DMA that flags the transfer error.

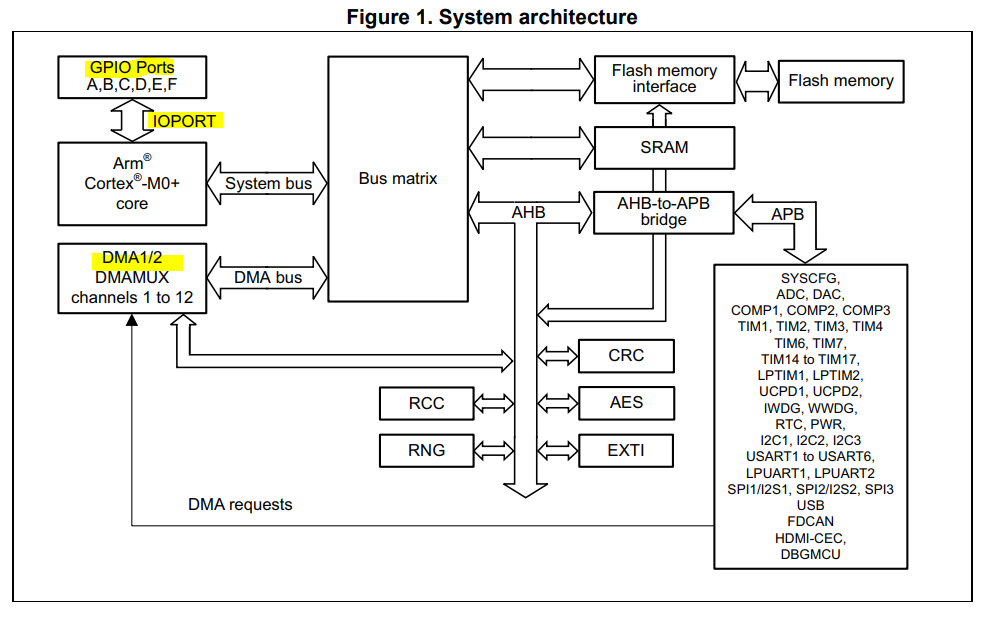

Can anyone confirm that this is the case? From the reference manual, it seems that DMA and GPIO are in different bus that makes my intention impossible.

Rgds

Calvin

- Labels:

-

DMA

-

GPIO-EXTI

-

STM32G0 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-04 5:16 AM

You should be able to do DMA transfers from memory to GPIOB->BSRR without issue. What error is it giving you?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-04 5:35 AM

Read out and post content of DMAMUX and DMA registers.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-04 8:20 AM

I can only see both the GIF and TEIF flags in the DMA ISR register set, implying the transfer error. With the DMA CNDTR remains unchanged. Meaning that the transfer error happens at the 1st data transfer (from memory to GP!OA BSRR).

Note: If I change the destination as memory and do memory to memory transfer, the code works.

But looking from the reference manual - RM0454 section 2, the diagram shows GPIO port bus and DMA bus may not be "connected".

I am off work until next Monday, so I can only get the register details by then.

Calvin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-04 8:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-04 9:44 AM

Indeed - the 'G0 (as well as 'L0) is Cortex-M0+ which has a special port on the processor for GPIO, so you can't DMA onto GPIOs.

My mistake too... :)

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-03-24 7:11 AM

This happened to me today. Glad to find an answer. =) But unhappy I can't trigger DMA to GPIO using a timer. :loudly_crying_face:

"I/O ports are directly connected to the single-cycle IO port bus. This allows fast I/O pin operations, e.g. toggling of the pin every two clock cycles. No conflict with the DMA can occur because this Cortex®-M0+ port is private to the CPU."

- How to translate ILI9341 driver in touchgfx project to HAL version? in STM32 MCUs TouchGFX and GUI

- Slave I2C fails to connect on stm32g030 in STM32 MCUs Products

- STM32H7S3V8T6 timer triggered DMA in STM32 MCUs Embedded software

- STM32G030 REV_ID Y, Z version error when loading the same firmware in STM32 MCUs Embedded software

- STM32U575: GPIOx->BSRR assignment causes reset - but only when debugging in STM32 MCUs Products