- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- LSERDY: long startup delay, when LSE in bypass mod...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LSERDY: long startup delay, when LSE in bypass mode driven by a slow clock

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-09 4:59 AM

Hi,

I've an application where I'd like to use LSE in passive mode driven by a slow (1Hz) signal.

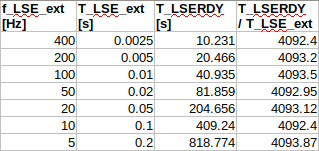

When testing bypass mode LSE with slow clocks, I observed long delays between startup (cold start) and LSERDY being set by hardware. When measuring that delay systematically, the results suggest that the hardware needs 4096 LSE clock cycles to set LSERDY

(See screenshot below with measurements at different frequencies of fLSE_ext)

Until LSERDY is set by hardware, LSE seems to be not passed through to the on-chip logic, and if LSE is driven with a 1Hz signal as I intended, then the chip will, on cold boot, need over 1 hour to enable LSE, which is kind of a show stopper.

So is there a workaround that allows the LSE in bypass mode to be used without waiting for LSERDY, or one to accelerate the LSE clock validation process?

As LSERDY seems to be intended to wait for the _crystal_ to stabilize, maybe it is overkill to use it for LSE bypass mode anyway.

Thanks, Patrick

BTW, I tested/observed this on a Nucleo-L433RC-P and the chip used for the target hardware will be a L431 (if that matters).

- Labels:

-

RCC

-

STM32L4 series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-09 7:16 AM

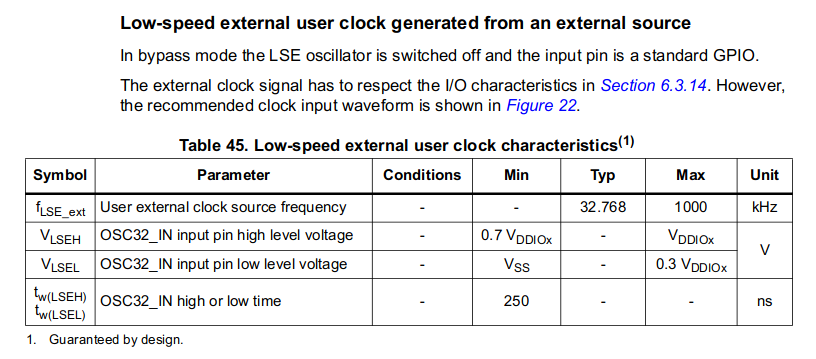

The datasheet specifies 1 to 1000 kHz as external LSE, But with 1 khz thi will also be about 2.5 seconds, a substantial delay.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-09 8:07 AM

4 seconds at 1 KHz ;)

where did you find 1KHz as minimum freq. for LSE?

in STM32L431xx datasheet, it mentions no minimum limit for LSE freq. in bypass mode

(page 115)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-09 11:19 AM

I doubt there is any easy workaround, and I'm afraid you'll need some external circuitry to achieve the first 4096 or so cycles fast enough.

As you might have noticed, this is primarily a user-driven forum with casual ST presence. If you need confirmation from ST, you should perhaps contact them directly, through FAE, or through the web support form (if it still exists).

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-09 11:26 AM

@Uwe Bonnes ,

in https://community.st.com/s/question/0D50X0000AiypntSQA/should-lserdy-assert-with-lsebyp you've mentioned that you've never seen LSERDY to set when using LSEBYP.

But patrislav here says, that LSE is not propagated to the RTC until LSEBYP is set.

So, were you successful in using the MEMS oscillator as you've mentioned in that thread?

Thanks,

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-10 2:04 AM

I minimum LSE value I took from the STM32L053 datasheet. For LSERDY not assering in some situation, I have follwing remarks in my code:

+ RCC_BDCR = 0;

+ if (LSE_BYPASS) {

+ /* L412 seem not to set LSERDY when LSE starts after LSEON.

+ * Busy wait until LSE RDY is set */

+ do {

+ /* LSEBYP must be set with LSEON de-asserted!*/

+ do {

+ RCC_BDCR &= ~RCC_BDCR_LSEON;

+ } while (RCC_BDCR & RCC_BDCR_LSEON);

+ do {

+ RCC_BDCR = RCC_BDCR_LSEBYP;

+ } while (~RCC_BDCR & RCC_BDCR_LSEBYP);

+ do {

+ RCC_BDCR = bdcr_new;

+ } while (~RCC_BDCR & RCC_BDCR_LSEON);

+ /* LSERDY takes 6 lse clocks.*/

+ for (int i = 0; (i < 1000) && (~RCC_BDCR & RCC_BDCR_LSERDY); i++);

+ } while (~RCC_BDCR & RCC_BDCR_LSERDY);

+ } else {

+ RCC_BDCR = bdcr_new;

+ }

with bdcr_new the assembled value fir BDCR.

- STM32H747 RTC weird behaviour: the display appears with abnormal characters in STM32 MCUs Embedded software

- STM32L562: frequency error when outputting LSE via MCO (crystal mode); bypass OK in STM32 MCUs Products

- Calibrating the STM32's real-time clock (RTC) in STM32 MCUs Products

- STM32H573 with Secure Manager, non-secure app can't switch LSE as RTC clock in STM32 MCUs Security

- GPIO , Button detection with interrupt ( USER1) on STM32N6570-DK in STM32 MCUs Embedded software