- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- STM32F767 SRAM problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F767 SRAM problem

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-28 12:25 AM

Hello, i made my own devkits with huge altera and STM32F4/7 micro-controllers.

As usual, STM32F479 performing very well, it uses 26b ADR, 32b data lines directly to FPGA.

But for some reason code generated by STM32CubeMX does not want to work. I mapped 4 banks of SRAM 16Mx32b to SRAM controllers, but they don't work, at all.

I am using this code to test it:

&sharpdefine Bank1_SRAM1_ADDR ((uint32_t)0x60000000) // FPGAvolatile uint32_t FMC_ADR_R = 0;

volatile uint32_t FMC_ADR_W = 0;

volatile uint32_t FMC_R = 0; volatile uint32_t FMC_W = 0; while (1) { *(uint32_t *) (Bank1_SRAM1_ADDR+FMC_ADR_W*4) = FMC_W;*(uint32_t *) (Bank1_SRAM1_ADDR+0) = 0;

FMC_R = *(uint32_t *) (Bank1_SRAM1_ADDR+FMC_ADR_R*4);

}

By using debugger, i am changing FMC_ADR_R, FMC_ADR_W, FMC_W values, and CS goes only single time low during init, after that it keeps high. Adding more delay did not helped between read writes, so i don't know whats hoing on.

Also, in migration documentations i read that it only have single sram controller ( chip select) while STM32F4XX does have 4, whats up to that ? so why CubeMX is very happy generating code for all 4 chip selects ?

Page 24

Any one knows whats going on ?

My sram init looks like this:

FMC_NORSRAM_TimingTypeDef Timing;

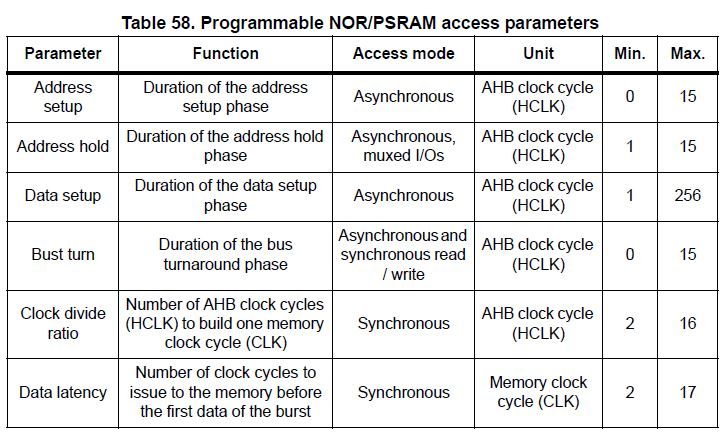

/** Perform the SRAM1 memory initialization sequence

*/ hsram1.Instance = FMC_NORSRAM_DEVICE; hsram1.Extended = FMC_NORSRAM_EXTENDED_DEVICE; /* hsram1.Init */ hsram1.Init.NSBank = FMC_NORSRAM_BANK1; hsram1.Init.DataAddressMux = FMC_DATA_ADDRESS_MUX_DISABLE; hsram1.Init.MemoryType = FMC_MEMORY_TYPE_SRAM; hsram1.Init.MemoryDataWidth = FMC_NORSRAM_MEM_BUS_WIDTH_32; hsram1.Init.BurstAccessMode = FMC_BURST_ACCESS_MODE_DISABLE; hsram1.Init.WaitSignalPolarity = FMC_WAIT_SIGNAL_POLARITY_LOW; hsram1.Init.WaitSignalActive = FMC_WAIT_TIMING_BEFORE_WS; hsram1.Init.WriteOperation = FMC_WRITE_OPERATION_DISABLE; hsram1.Init.WaitSignal = FMC_WAIT_SIGNAL_DISABLE; hsram1.Init.ExtendedMode = FMC_EXTENDED_MODE_DISABLE; hsram1.Init.AsynchronousWait = FMC_ASYNCHRONOUS_WAIT_DISABLE; hsram1.Init.WriteBurst = FMC_WRITE_BURST_DISABLE; hsram1.Init.ContinuousClock = FMC_CONTINUOUS_CLOCK_SYNC_ASYNC; hsram1.Init.WriteFifo = FMC_WRITE_FIFO_DISABLE; hsram1.Init.PageSize = FMC_PAGE_SIZE_NONE; /* Timing */ Timing.AddressSetupTime = 5; Timing.AddressHoldTime = 3; Timing.DataSetupTime = 5; Timing.BusTurnAroundDuration = 0; Timing.CLKDivision = 0; Timing.DataLatency = 0; Timing.AccessMode = FMC_ACCESS_MODE_A; /* ExtTiming */if (HAL_SRAM_Init(&hsram1, &Timing, NULL) != HAL_OK)

{ _Error_Handler(__FILE__, __LINE__); }Also, i was messing with timing, it does not help at all :\#error #fmc #sram #problem #cubemx- Labels:

-

FMC-FSMC

-

STM32CubeMX

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-28 8:56 AM

Hello!

I dont have your hardware to reproduce the error but in your initialisation you put FMC_WRITE_OPERATION_DISABLE

This is 'write protect ' functionality.

*(uint32_t *) (Bank1_SRAM1_ADDR+FMC_ADR_W*4) = FMC_W;

*(uint32_t *) (Bank1_SRAM1_ADDR+0) = 0;

You try to Write.

It will help the community if you post the .IOC file

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-28 9:02 AM

Well spotted, while in cubemx it was disabled.

Also i did use function to disable it ( called from sram driver, don't remember prototype), but had no effect, but all right, will try to edit my sram init file, maybe it will help.But it should be reading, but it is not, stays high all the time, while with STM32F4 i get around 20MHz- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-28 11:15 AM

check your call Timing initialisation function

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-31 1:01 AM

Just like i suspected, after generating sram init code i change write to enable, so this is not a problem.

FMC_NORSRAM_TimingTypeDef Timing;

/** Perform the SRAM1 memory initialization sequence

*/ hsram1.Instance = FMC_NORSRAM_DEVICE; hsram1.Extended = FMC_NORSRAM_EXTENDED_DEVICE; /* hsram1.Init */ hsram1.Init.NSBank = FMC_NORSRAM_BANK1; hsram1.Init.DataAddressMux = FMC_DATA_ADDRESS_MUX_DISABLE; hsram1.Init.MemoryType = FMC_MEMORY_TYPE_SRAM; hsram1.Init.MemoryDataWidth = FMC_NORSRAM_MEM_BUS_WIDTH_32; hsram1.Init.BurstAccessMode = FMC_BURST_ACCESS_MODE_DISABLE; hsram1.Init.WaitSignalPolarity = FMC_WAIT_SIGNAL_POLARITY_LOW; hsram1.Init.WaitSignalActive = FMC_WAIT_TIMING_BEFORE_WS; hsram1.Init.WriteOperation = FMC_WRITE_OPERATION_ENABLE; hsram1.Init.WaitSignal = FMC_WAIT_SIGNAL_DISABLE; hsram1.Init.ExtendedMode = FMC_EXTENDED_MODE_DISABLE; hsram1.Init.AsynchronousWait = FMC_ASYNCHRONOUS_WAIT_DISABLE; hsram1.Init.WriteBurst = FMC_WRITE_BURST_DISABLE; hsram1.Init.ContinuousClock = FMC_CONTINUOUS_CLOCK_SYNC_ONLY; hsram1.Init.WriteFifo = FMC_WRITE_FIFO_DISABLE; hsram1.Init.PageSize = FMC_PAGE_SIZE_NONE; /* Timing */ Timing.AddressSetupTime = 10; Timing.AddressHoldTime = 10; Timing.DataSetupTime = 10; Timing.BusTurnAroundDuration = 1; Timing.CLKDivision = 1; Timing.DataLatency = 1; Timing.AccessMode = FMC_ACCESS_MODE_A; /* ExtTiming */if (HAL_SRAM_Init(&hsram1, &Timing, NULL) != HAL_OK)

{ _Error_Handler(__FILE__, __LINE__); }But why is it ? Even original example with sram does not generate any signals, maybe it is because IAR ARM 8.2 ?

I did try to change optimization levels, no response, same chip select behavior. Also i did check gpio init code, it does enable chip select pin, and it does enable that pin clock ( even if i have only chip select enabled as AF, it will generate signals, while complete SRAm interface will be dead, i understand that) Also, it does read single time correctly, in FPGA i have current FW version number, and it does read it, but only single time. Strange thing is that address should be 0, but it reading that number at address 1 (((uint32_t)0x60000004) But again, why only single time ? :\ Attached my complete generated code from STM32CubeMx, maybe some one could take a look, or it is another fabulues times of STM32CubeMx not working ?For the love of god, ST, produce SPL libraries for F7 and H7 micro controllers, since i am afraid of using them, and will stick to STM32F4 series instead

:(

And they are getting quite slow in comparison of H7 and F7 ________________ Attachments : STM32F767NIH.rar : https://st--c.eu10.content.force.com/sfc/dist/version/download/?oid=00Db0000000YtG6&ids=0680X000006HyXK&d=%2Fa%2F0X0000000b9D%2FGPAp9lsvF_kfDJZlfHVi5c8Gvv5DvyxtJ_XS0E1ajYw&asPdf=false- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-02 6:42 AM

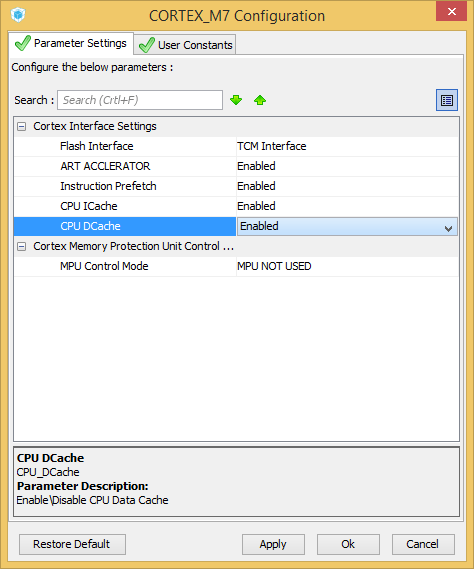

Please CubeMX programmers, produce fail safe CPU parameters, so if one is selected, others could not be enabled !!

Please CubeMX programmers, produce fail safe CPU parameters, so if one is selected, others could not be enabled !!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-02 6:31 PM

Excellent work !

please reiterate to enlighten us all

'The correct answer i was enabled D and I cache at the same time with accelerator, and it cause this.' ( this and accelerator ??)

when you have the ART Accelerator ON, D-Cache ON I-Cache ON, then .. what doesn't work ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-03 6:38 AM

when you have the ART Accelerator ON, D-Cache ON I-Cache ON, then .. what doesn't work ?

my external 32b SRAM interface does not work, while at the same time, debugger shows that every thing is ok.

It just does not want to generate any hardware signals, same code, commented DI init functions, and viola, works like a charm- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-03 7:06 AM

Or to be more precise, i can't use //SCB_EnableDCache();, since it will stop my SRAM interface working.

Any ideas why it is happening?- STM32C091GCU6: STM32IDE's flash upload is limited to 128KB. in STM32CubeIDE (MCUs)

- Failed to implement external loader on custom board in STM32CubeProgrammer (MCUs)

- STM32L431CBT6 Debugger Breaks in System Memory (0x1FFF...) After Fixing Programmer XML in STM32CubeProgrammer (MCUs)

- DEV_TARGET_NOT_HALTED in STM32CubeIDE (MCUs)

- CubeMx does not configure FileX properly - Bugs in STM32CubeMX (MCUs)