- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- STM32CubeMX 6.10.0 limit source frequency for ADC

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32CubeMX 6.10.0 limit source frequency for ADC

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-24 4:53 AM - edited 2023-11-24 4:55 AM

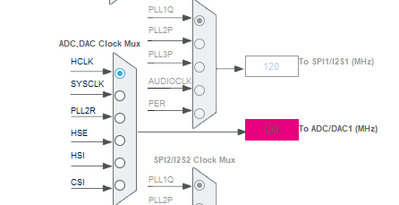

I am trying to configure ADC for STM32H562VGT in STM32CubeMX but it is limiting maximum source frequency for ADC. It limits it to 75MHz (which is maximum frequency of ADC clock) but ADC clock has its internal divider.

For example I want to use 120MHz HCLK as a source for ADC clock and set internal divider to 64 but Cube is notifying me with Clock issues.

In version 6.8.0 this problem was not present and I could use 120MHz clock as clock source for ADC.

Is it some bug in new version of Cube?

- Labels:

-

STM32H5 series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-24 5:13 AM - edited 2023-11-24 5:17 AM

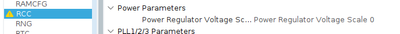

the max clock depends on core voltage setting - cube shows/limits according to this setting.

ie

set to scale0 for max frequencies. .... and max power consumption. :)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-24 8:17 AM

Hello @BlazejKrysztofiak

First let me thank you for posting!

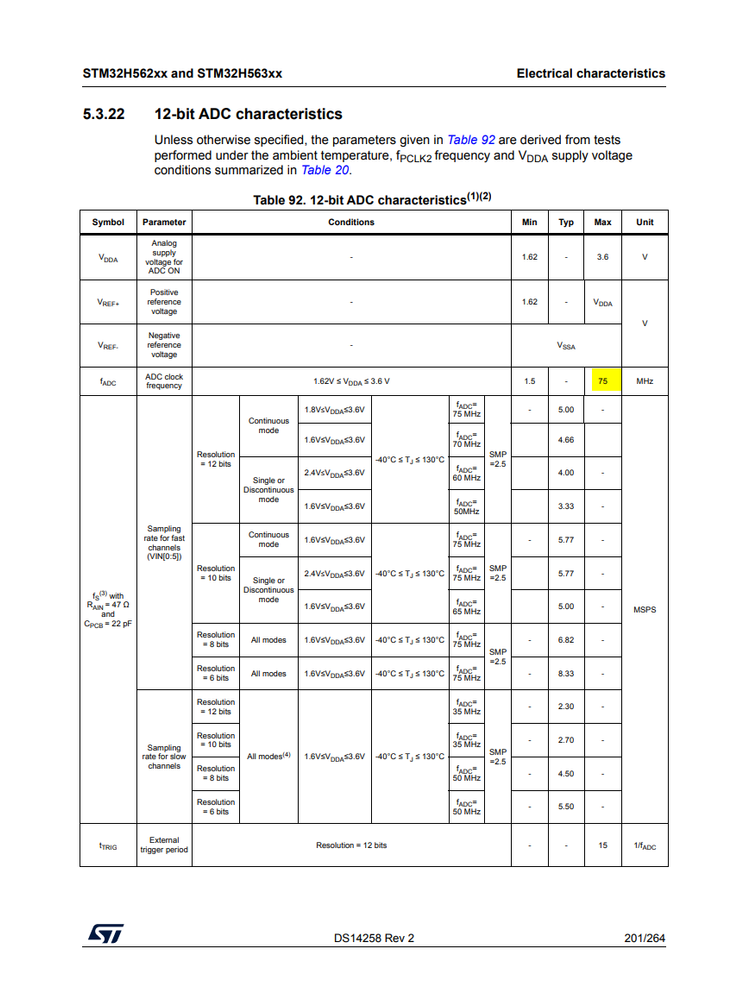

As per DS14258 it is mentioned that the maximum source frequency for ADC is 75Mhz.

This fix was added in the last version 6.10 to ensure that CubeMX will be aligned with the Datasheet.

Thank you!

Souhaib

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-26 11:28 PM

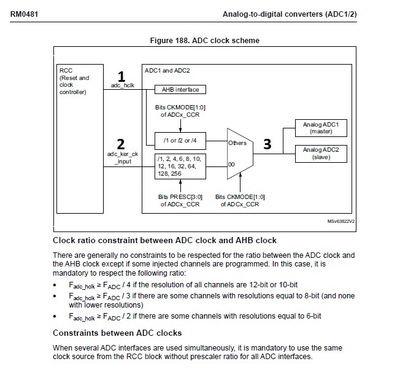

@Souhaib MAZHOUD I thought that this restriction applies directly to ADC clock (3) no to clock from which ADC clock is derived (1 or 2) because 1 or 2 can be further divided to achieve lower frequency of ADC and as for now Cube doesn't let me set 2 frequency higher than 75MHz no matter what divider I set for ADC clock.

Also this restriction can be still omitted by using 1 as clock source because we can set hclk to frequency higher than 75MHz and we can use divider set to 1 and Cube lets us do it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-26 11:29 PM - edited 2023-11-26 11:29 PM

Thank you for answering but in my case it doesn't make difference.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-26 11:55 PM - edited 2023-11-26 11:58 PM

right. (i tried on my H563 nucleo board now).

i think, Cube is wrong here, on V 6.9.1 (i use here) , allowing 125MHz for ADC. (250M /2 setting).

and your V 6.10. also wrong... :)

for my understanding the ADC can work with max. 75MHz, (pos. 3 in your pic from rm);

and input clk (pos. 1 or 2 ) can be divided down to meet this.

so @Souhaib MAZHOUD is also wrong, because 75M is just the max clk for ADC, not for input to the ADC prescaler. He says same as Cube V 6.10. : limit the adc_ker_clk to 75M, but it should just limit the ADC_clk to 75M by setting the prescaler correct.

- Cannot find/enable CMSIS-DSP (arm_math.h) on STM32N6570-DK via STM32CubeMX in STM32CubeMX (MCUs)

- STM32H743 - Setting External Event source for HRTIM Timer in CubeMX ? in STM32CubeMX (MCUs)

- STM32CubeMX 6.17.0 generated project lost <root folder> in STM32CubeMX (MCUs)

- Clock configuration in STM32CubeMX2 (MCUs)

- GCC -O2 optimization ~3% lower performance than Keil for motor control application in STM32CubeIDE (MCUs)