- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- Can stm32F446 TIM2 run at 180Mhz

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Can stm32F446 TIM2 run at 180Mhz

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-24 2:49 AM

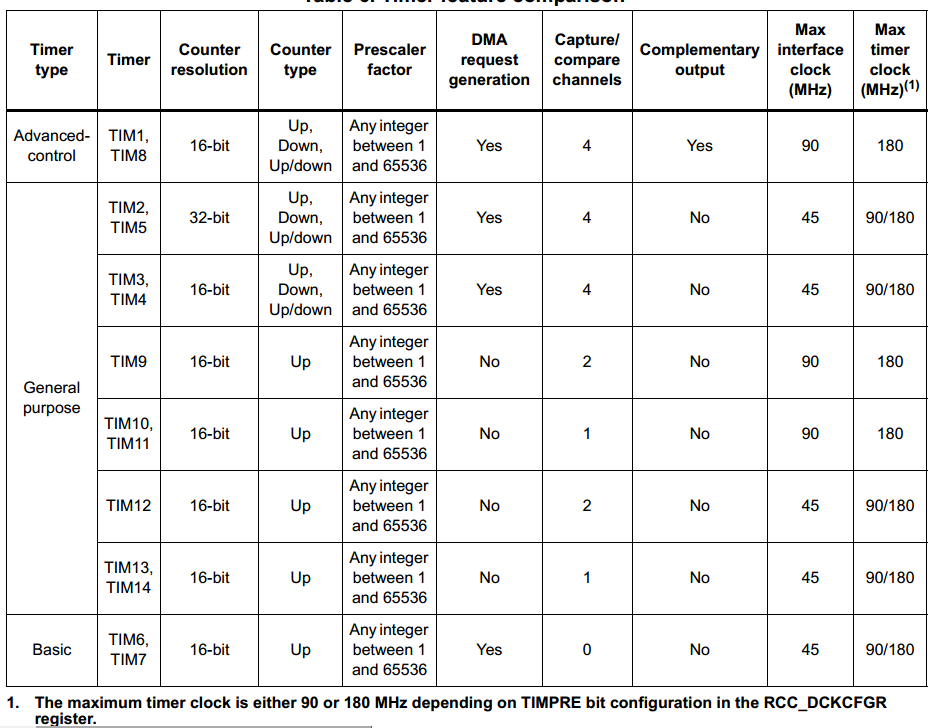

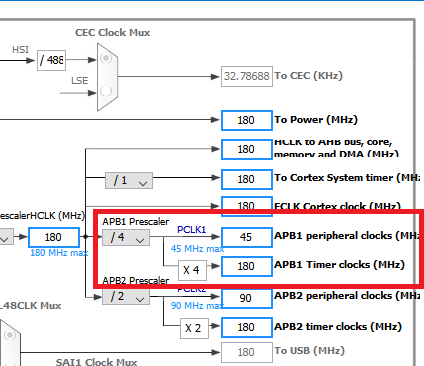

Hi, I've got this from the F446 data sheet.

I hope that I can run TIM2 at 180Mhz

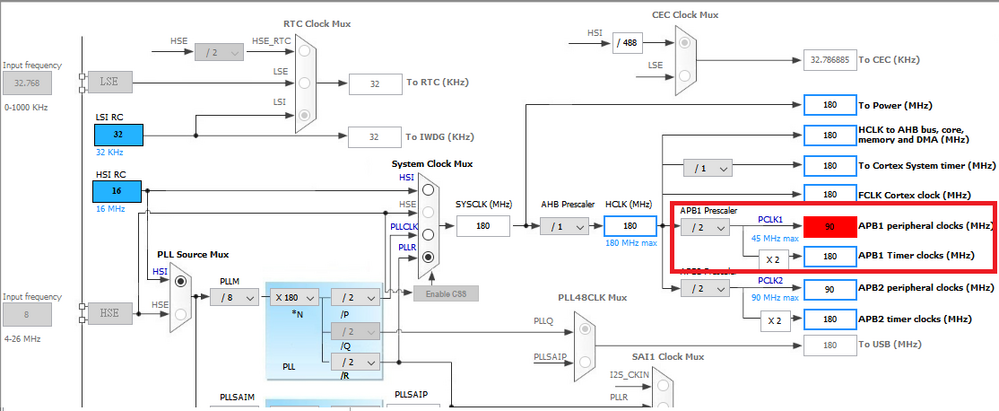

However, it seems that APB1 peripheral CLK can only run at 90Mhz as the cubeMX indicates as followed:

So can I really make TIM2 run at 180MHz or not?!

Thanks for reading!

,Zt

#tim2 #stm32f4 #clock-configuration #cube-mx #stm32f446Solved! Go to Solution.

- Labels:

-

STM32CubeMX

-

STM32F4 Series

-

TIM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-25 2:43 AM

Sorry, I didn't read your original question properly.

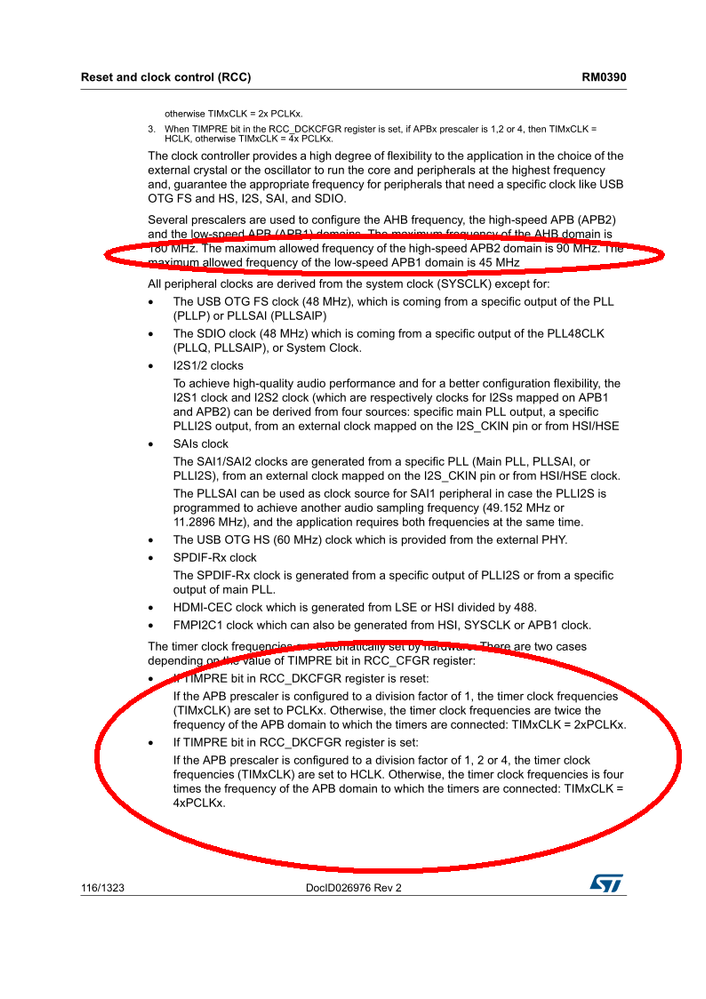

As you can see in that clock tree above, all TIMx timers have a clock separate from their respective APB clock. The APB clock still determines the access to their registers through the respective APB bus, but their internal clock input runs from that separate clock. Electrically, all TIMx timers are capable of running their internal clock input at 180MHz, see datasheet chapter 6.3.19 TIM timer characteristics.

The APB clocks can't run as high as the AHB clock i.e. at 180MHz, they have to be divided. If that divider is 2 and RCC_DCKCFGR.TIMPRE = 0, the timer clock is 2x APB clock, i.e. equal to AHB clock. If the divider is 1, 2 or 4 and RCC_DCKCFGR.TIMPRE = 1, the timer clock is equal to AHB clock.

However, the maximum clock for APB1 is 45MHz, i.e. if AHB clock is 180MHz, APB1 divider must be at least 4.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-24 5:32 AM

Yes.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-24 8:06 PM

Thanks for reply, JW!

It seems that i misunderstood somethins.

:(

So TIM2 can run at 180MHz, what about APB1 peripheral clock limitataion?

Can TIM2(or APB1 clock) run at 180Mhz, and APB1 peripheral clock run at 90Mhz simultaneously?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-25 2:43 AM

Sorry, I didn't read your original question properly.

As you can see in that clock tree above, all TIMx timers have a clock separate from their respective APB clock. The APB clock still determines the access to their registers through the respective APB bus, but their internal clock input runs from that separate clock. Electrically, all TIMx timers are capable of running their internal clock input at 180MHz, see datasheet chapter 6.3.19 TIM timer characteristics.

The APB clocks can't run as high as the AHB clock i.e. at 180MHz, they have to be divided. If that divider is 2 and RCC_DCKCFGR.TIMPRE = 0, the timer clock is 2x APB clock, i.e. equal to AHB clock. If the divider is 1, 2 or 4 and RCC_DCKCFGR.TIMPRE = 1, the timer clock is equal to AHB clock.

However, the maximum clock for APB1 is 45MHz, i.e. if AHB clock is 180MHz, APB1 divider must be at least 4.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-25 4:53 AM

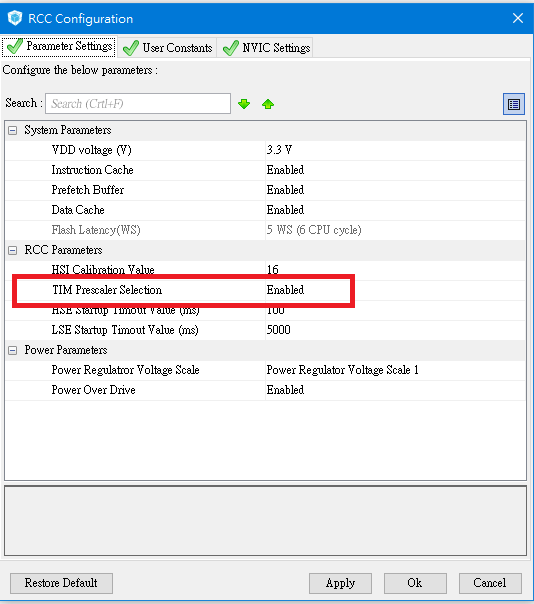

Hey, I finally got it!

I am such an idiot!!

Once I did the following,

I got the clock tree distribution, haha!

Never blame CubeMx in the very beginning!