- STMicroelectronics Community

- STM32 MPUs

- STM32 MPUs Products

- Re: How to improve the USB OTG speed of STM32MP157...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to improve the USB OTG speed of STM32MP157?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-18 3:38 AM

The hardware is STM32MP157C-DK2 board.

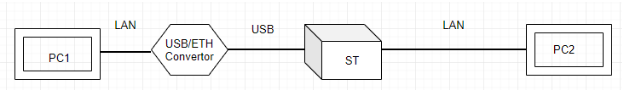

1. We setup the test environment as below:

We bridge the USB port and the Ethernet port in the ST.

The throughput is about 270Mbit/sec(Limited by the usb to Ethernet convertor).

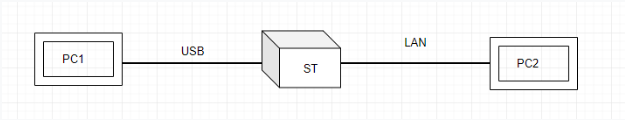

2. Another test environment is:

The ST is using the USB gadget functions. The USB port and the Ethernet port are bridged.

Result:

RNDIS: 90Mbit/sec.

CDC-EEM: 110Mbit/sec.

CDC-ECM: 135Mbit/sec.

The performance is not good enough compared to test1.

Is the speed limited by the USB-OTG controller(dwc2)?

Can we change the DMA settings in the dwc2 ?

Or anyway to improve the throughput?

Please help!

Thank you very much.

- Labels:

-

STM32MP15 Lines

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-10 8:27 AM

Hi,

The way to improve the throughput is to tune FIFO size in the OTG IP. It can be done through kernel device tree.

In usbotg_hs entry of arch/arm/boot/dts/stm32mp157c.dtsi :

usbotg_hs: usb-otg@49000000 {

compatible = "st,stm32mp1-hsotg", "snps,dwc2";

reg = <0x49000000 0x10000>;

clocks = <&rcc USBO_K>;

clock-names = "otg";

resets = <&rcc USBO_R>;

reset-names = "dwc2";

interrupts-extended = <&intc GIC_SPI 98 IRQ_TYPE_LEVEL_HIGH>,

<&exti 44 1>;

interrupt-names = "event", "wakeup";

g-rx-fifo-size = <256>;

g-np-tx-fifo-size = <32>;

g-tx-fifo-size = <128 128 64 64 64 64 32 32>;

dr_mode = "otg";

usb33d-supply = <&usb33>;

power-domains = <&pd_core>;

wakeup-source;

status = "disabled";

};The following patch increases tx troughput (I measured a gain of 12% in TX):

- g-np-tx-fifo-size = <32>;

- g-tx-fifo-size = <128 128 64 64 64 64 32 32>;

+ g-np-tx-fifo-size = <256>;

+ g-tx-fifo-size = <128 128 64 16 16 16 16 16>The sum of all FIFO size must be lower than 952.

Depending on your use case, you can tune FIFO sizes to get the best compromise.

BR,

Christophe

- Is there anyway to improve graphcis speed on STM32MP1? in STM32 MPUs Embedded software and solutions

- I2C Configuartion in STM32 MPUs Embedded software and solutions

- STM32MP157 custom board TF-A SDMMC init failed in STM32 MPUs Embedded software and solutions

- STM32CubeProgrammer on timeout for STM32MP1 in STM32 MPUs Embedded software and solutions

- STM32MP1 ethernet issue in STM32 MPUs Products