- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs TouchGFX and GUI

- Re: STM32H743: FMC SDRAM access too slow for LTDC ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H743: FMC SDRAM access too slow for LTDC @ 25MHz

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-07 03:15 AM

I've copied all the various examples of using LTDC to drive a VGA screen and implemented them on the STM32H743II with 64Mbit SDRAM using the normal SDRAM timings. Everything works except that the RAM reading is too slow to keep up with the LTDC requests resulting in data corruption on the screen. This is proved by slowing down the request rate when everything works perfectly (12.5MHz). I've looked at the reference manual and the datasheet but can't work out what drives the FMC clock - is it fixed frequency , if so what?

Any pointers appreciated - surely an H743 @ 400MHz should be able to do this when lot of people have it working on the STM32F429.

Solved! Go to Solution.

- Labels:

-

FMC-FSMC

-

LCD-LTDC

-

STM32H7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-07 03:55 AM

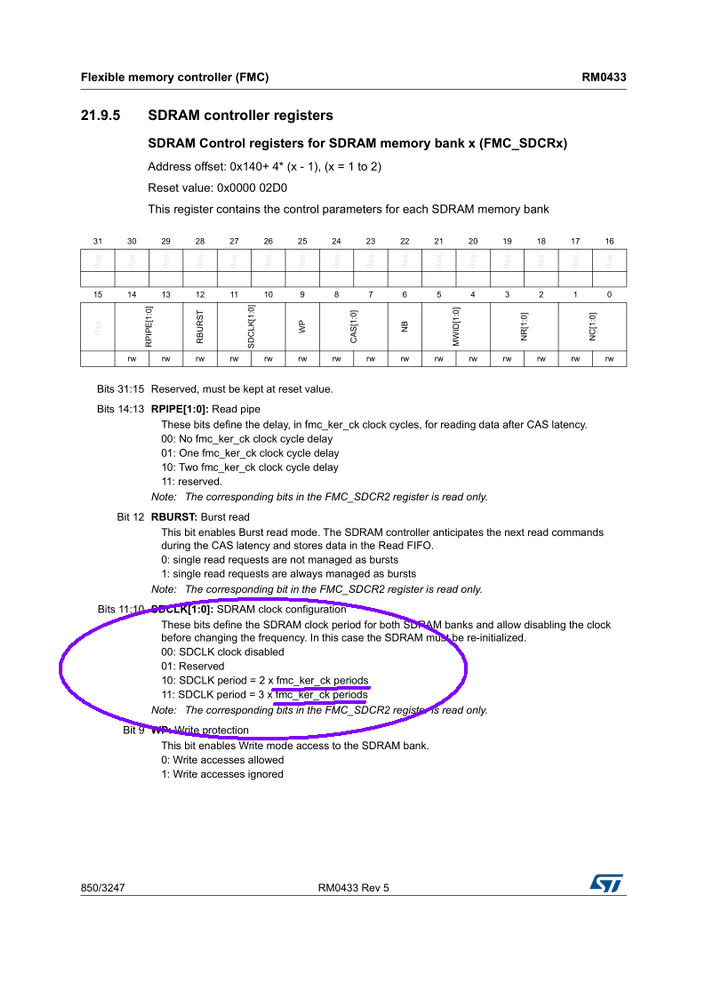

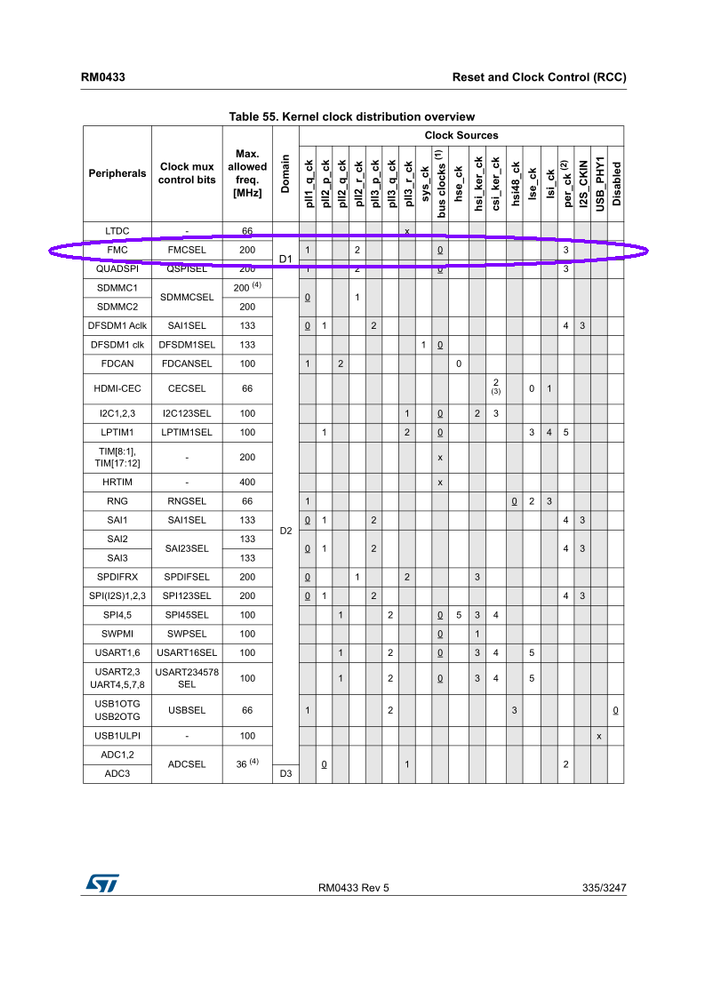

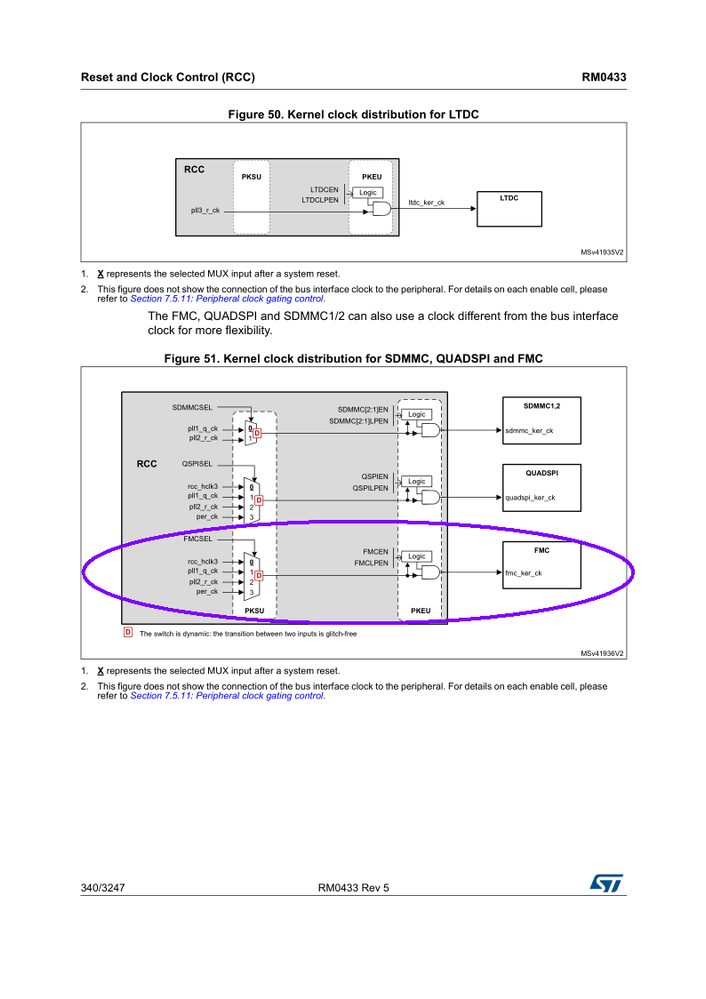

> I've looked at the reference manual and the datasheet but can't work out what drives the FMC clock

And what exactly did you look at?

> surely an H743 @ 400MHz should be able to do this when lot of people have it working on the STM32F429

This depends on several factors, the raw memory clock frequency vs pixel clock is just one of them. The main one is the used color depth. Bandwidth of SDRAM/FMC can be easily exhausted if there's a heavy fight for the resources (FMC access here) from various bus masters (LTDC, processor, DMA, DMA2D, maybe also others). Using FMC's other banks won't help either. IIRC, FMC in the 'F429 runs at the system clock, i.e. max. 180MHz, which is close to the max clock of FMC in the 'H7 (200MHz), so there's not much of a difference in this.

JW

PS. Have you read AN4861 ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-07 03:55 AM

> I've looked at the reference manual and the datasheet but can't work out what drives the FMC clock

And what exactly did you look at?

> surely an H743 @ 400MHz should be able to do this when lot of people have it working on the STM32F429

This depends on several factors, the raw memory clock frequency vs pixel clock is just one of them. The main one is the used color depth. Bandwidth of SDRAM/FMC can be easily exhausted if there's a heavy fight for the resources (FMC access here) from various bus masters (LTDC, processor, DMA, DMA2D, maybe also others). Using FMC's other banks won't help either. IIRC, FMC in the 'F429 runs at the system clock, i.e. max. 180MHz, which is close to the max clock of FMC in the 'H7 (200MHz), so there's not much of a difference in this.

JW

PS. Have you read AN4861 ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-07 04:52 AM

Many thanks

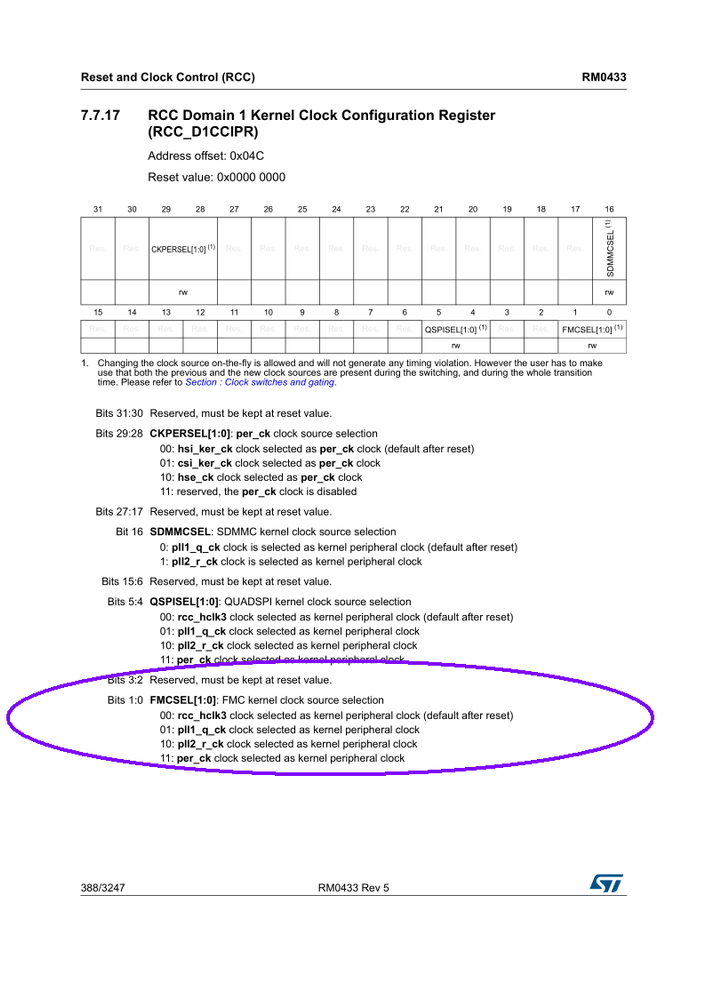

I found the reference to fmc_ker_ck but not the definition of where it comes from. In my application FMC was using the default clock which is in theory RCC_HCLK3 which is running at 200MHz. Changing this to PLL_q_clk which I have set for 200MHz has solved the issue ( RCC->D1CCIPR |=1;)

This doesn't make any sense but at least the problem is solved.

One additional confusion is the H743 Clock configuration page of CubeMX doesn't include FMC.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-02-21 05:53 PM

Sorry sir where i can set this in stmcubeide?

- Files for STM32H563 External Loader in STM32CubeIDE (MCUs)

- STM32H743 SPI DMA delay in STM32 MCUs Embedded software

- STM32H743 SPI with CRC mode, acces to CRC from frame in STM32 MCUs Products

- STM32H743 memory bandwidth issues with DCMI, FMC, ADC, parallel bus, DMA1, DMA2 / DCACHE issue in STM32 MCUs Embedded software

- Firmware update : Dual-Bank External Flash Management for TouchGFX Storage in STM32 MCUs TouchGFX and GUI