- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: X-CUBE-SOUNDTER1: how to set I2S clock?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

X-CUBE-SOUNDTER1: how to set I2S clock?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-29 1:47 PM

Hi, I have a nucleo f401re board and a x-nucleo-cca01m1 shield mounting STA350BW IC. Nucleo transmits data as a master to the shield using I2S half duplex communication. I want to know what is Master Clock's purpose on I2S bus. I understand that it stands for an external clock for STA350BW, doesn't it? So does the IC work on this clock?

In particular I want to understand the meaning of these settings referred to the master clock:

if (AudioFreq == 96000)

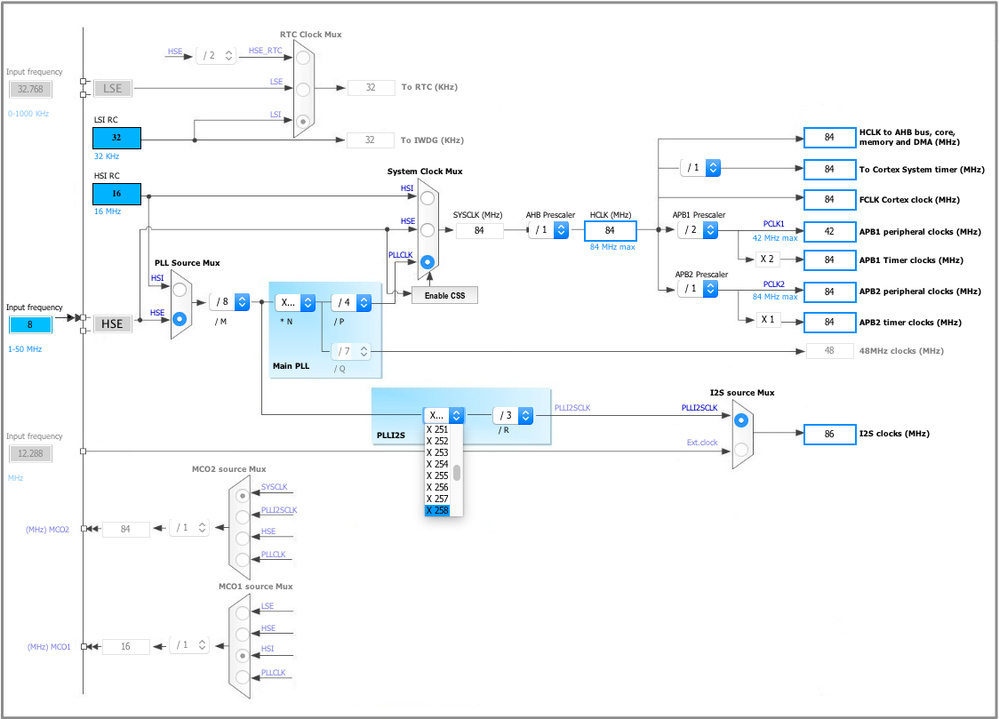

{ rccclkinit.PLLI2S.PLLI2SN = 344; rccclkinit.PLLI2S.PLLI2SR = 2; HAL_RCCEx_PeriphCLKConfig(&rccclkinit); } else if (AudioFreq == 48000) { rccclkinit.PLLI2S.PLLI2SN = 258; rccclkinit.PLLI2S.PLLI2SR = 3; HAL_RCCEx_PeriphCLKConfig(&rccclkinit); } else if (AudioFreq == 44100) { rccclkinit.PLLI2S.PLLI2SN = 271; rccclkinit.PLLI2S.PLLI2SR = 2; HAL_RCCEx_PeriphCLKConfig(&rccclkinit); } else if (AudioFreq == 32000) { rccclkinit.PLLI2S.PLLI2SN = 213; rccclkinit.PLLI2S.PLLI2SR = 2; HAL_RCCEx_PeriphCLKConfig(&rccclkinit); }(x_nucleo_cca01m1_audio_f4.c)

Thanks for any answers. Best regards.

#x-cube-cca01m1 #i2s #nucleo-401 #x-cube-soundter1- Labels:

-

I2S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-29 7:47 PM

N is a multiplier, R is a divisor. its slowing down the i2s clock when the audio frequency is lower. plug your values into the STM32CubeMX application's Clock Configuration pane and you can see the changes to the i2s clock frequency.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-29 11:23 PM

So the general rule is lower is sampling frequency, slower should be the master clock. Are there amy other constraints? Looking at

STA350BW's datasheet some internal clock's frequencies are fixed in reference to sampling frequencies. Is there a link with master clock?

PS in 44800 Hz case, clock seems slower than 44100 Hz case.

Thanks you for the answer

- STM32G0B1 Timer 6 - program crash when timer started with interrupt in STM32 MCUs Products

- STM32L5 Stop2 and Comparator in STM32 MCUs Products

- Low power STOP1 mode current consumption high in STM32 MCUs Products

- SD card on an STM32U5G9J-DK1 Discovery Kit in STM32 MCUs Boards and hardware tools

- I want to transmit adc values to hercules while using ibus protocol. in STM32 MCUs Embedded software