- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- [X-cube-AI] Does stm32 F/H arm coretex-M7 series h...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

[X-cube-AI] Does stm32 F/H arm coretex-M7 series hardware has TPU(tensor processing unit) for hardware accelation ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-07 6:47 PM

Hello.

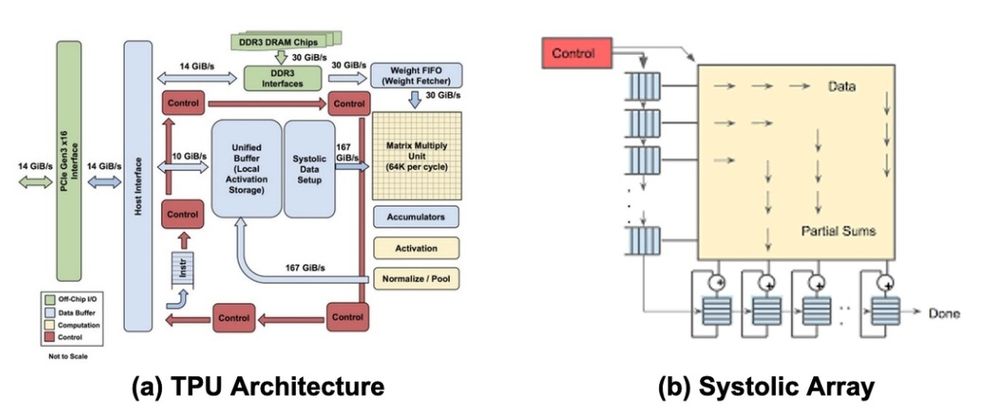

I want to know does stm32 cortex m7 series has TPU (tensor processing unit) for hardware acceleration. I heard that TPU has a systolic array which is a network of processors that are responsible for performing computations and passing the results across the system. It consists of a large number of processing elements(PEs) that are arranged in arrays, as illustrated above. These arrays have a high degree of parallelism and are favourable for parallel computing.

A typical Tensor Processing Unit(TPU) has two systolic arrays of size 128*128, so i think it can reduces cycles/ macc.

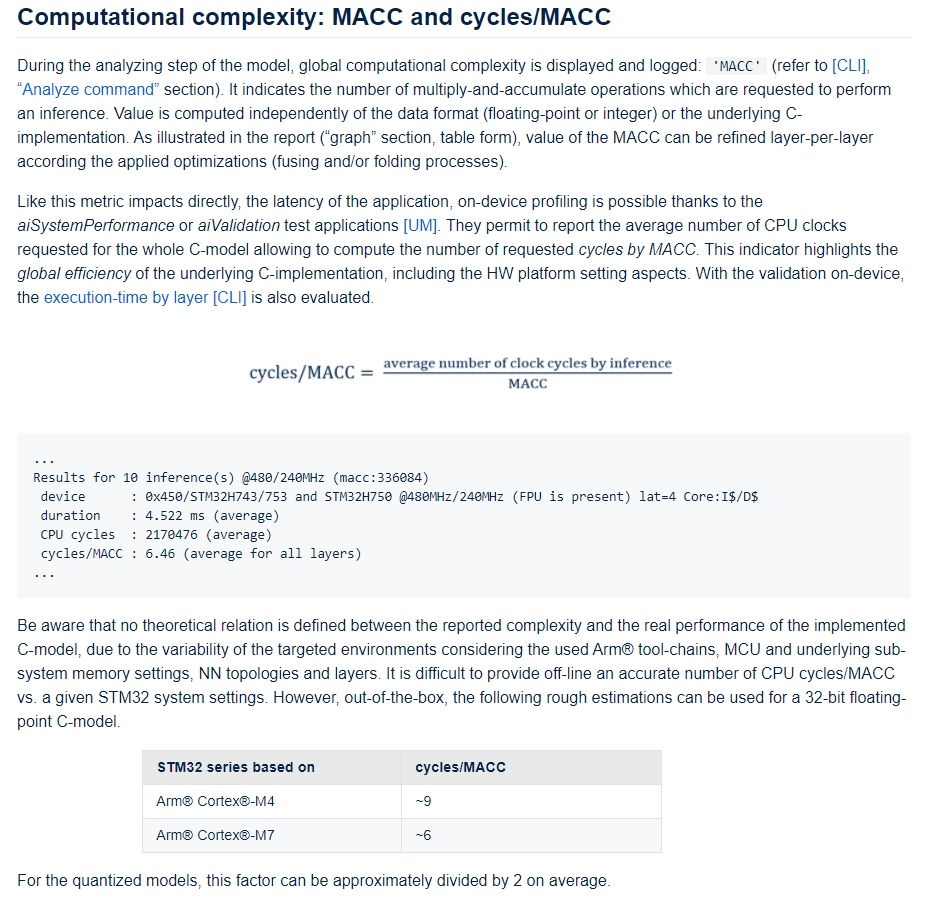

But in x-cube-ai documents, it is difficult to provide off-line an accurate number of CPU cycles/MACC. However, rough estimations for a 32-bit floating point C-model is ~6 cycles/MACC for Arm cortex-M7.

I think stm32 cortex m7 is just CPU not hardware accelerator. Is it right?

I want to clear explanation for this issue.

Best regards.

- Labels:

-

STM32F7 series

-

STM32H7 series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-07 7:37 PM

No

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-08 7:00 PM

Thank you for answer. The manuals are vast. If you don't mind, can you tell me where to look ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-08 7:11 PM

Doesn't Figure 1 diagram the core and the attached optional units? ITM, DWT, ETM,etc

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-09 1:54 AM

- STM32WBA63 + STM32_WPAN BLE + FreeRTOS tickless idle: BLE advertising misses LL timing after STOP wake when adding pre/post sleep hooks in STM32 MCUs Wireless

- Unexpected data corruption when camera and display both running (with SDRAM framebuffers in between) in STM32 MCUs Products

- STM32N6 JPEG encoder fails for any image width ≠ 800 (e.g., 480, 960) — IDMAEN auto-cleared, raw data dumped in STM32 MCUs Embedded software

- Recommendation on STM board with image processing capacities in Others: STM32 MCUs related

- STM32G4 I2C Slave AF Error on Normal Transaction Completion in STM32 MCUs Embedded software