What is the use of Clock Division settings ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-15 1:00 AM

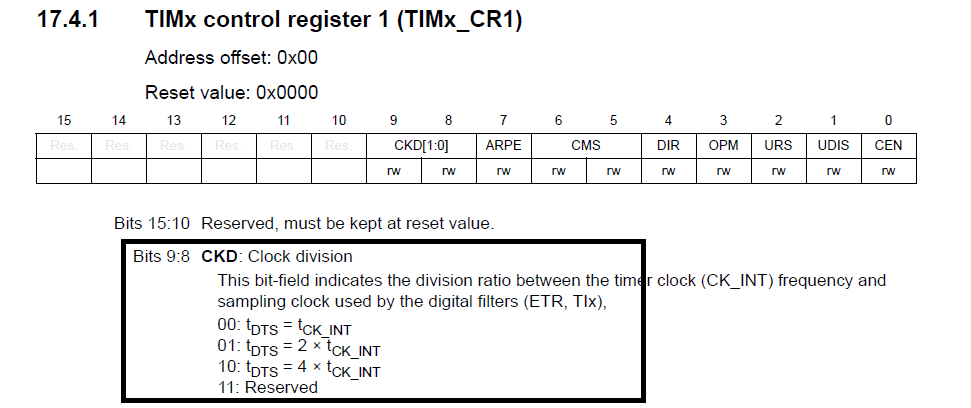

Hello, I am using TIM2 peripheral and many times f(DTS) is mentioned , what is that ?

also what is the purpose of clock division settings ?

does it divide the internal clock ? (CLK_INT)

#stm32f4 #timer

#stm32f4 #timer

Solved! Go to Solution.

- Labels:

-

STM32F4 Series

-

TIM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-15 3:49 AM

The ETR input and the channel's inputs have digital ('de-glitch') filters on them. The input clock to these filters may be a divided version of the timer's internal clock (i.e. the one which arrives from RCC); and this field determines the division ratio for those.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-15 3:49 AM

The ETR input and the channel's inputs have digital ('de-glitch') filters on them. The input clock to these filters may be a divided version of the timer's internal clock (i.e. the one which arrives from RCC); and this field determines the division ratio for those.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-21 6:59 AM

Thanks for your reply . makes sense now .