- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Using TIM5 for function call timing and not gettin...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Using TIM5 for function call timing and not getting expected results

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-12 6:05 PM

STM32F777

__HAL_RCC_TIM5_CLK_ENABLE();

TIM5->PSC = HAL_RCC_GetPCLK1Freq()/1000000 - 1;

TIM5->CR1 = TIM_CR1_CEN;

cyclecountstart = TIM5->CNT;

HAL_Delay(1);

cyclecountend = TIM5->CNT;

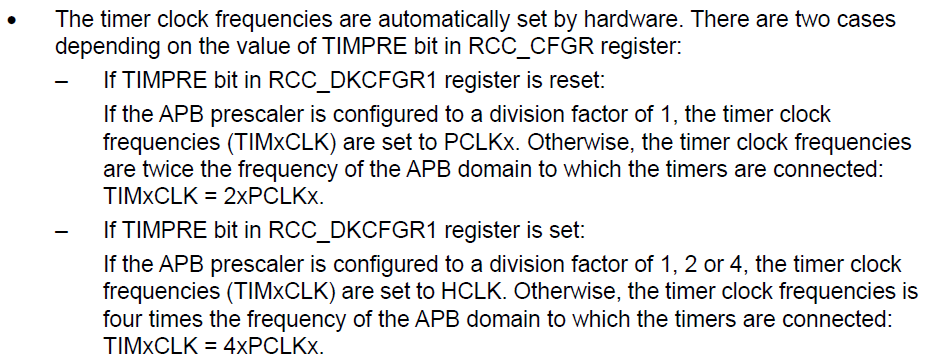

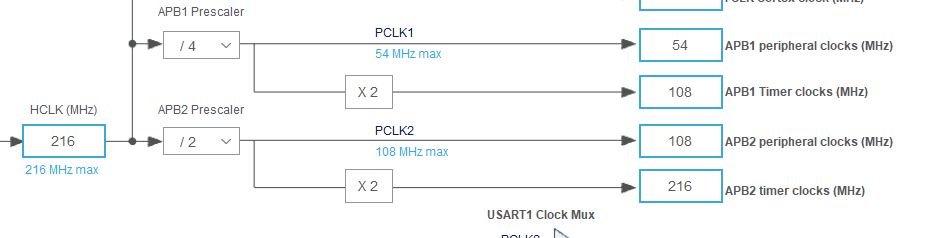

cyclecount = cyclecountend - cyclecountstart;I expect to see cyclecount to be somewhere in the neighborhood of 1000. Yes I know it could be as high as 2000. However, I consistently get around 168,000. I have verified prescaler is getting set how I expect (53 since PCLK1 is 54 MHz). If I remove the delay completely I see around 14 counts which I guess is believable but seems high.

What am I missing?

Solved! Go to Solution.

- Labels:

-

STM32F7 series

-

TIM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-13 12:59 AM

TIM_PSC is unconditionally preloaded, which means, that value written to it gets taken into account only after Update event, which usually means the nearest overflow/underflow. In your latter case with changing to downcounting you've effectively caused underflow just as the timer starts to run. As TIM5 is a 32-bit timer, even at the default no prescaler it takes considerable time until it overflows for the first time, when counting up.

The usual trick is to set TIM_EGR.UG to force an Update just after writing to TIM_PSC, but note that should you enable the Update interrupt, it would fire immediately.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-12 6:10 PM

Just want to add. Based on a search in these forums I changed the setting of CR1 to flip the DIR bit:

TIM5->CR1 = TIM_CR1_CEN | TIM_CR1_DIR;Changing to subtract end from start because we are down-counting now, I get a "somewhat" reasonable 3100 counts. Why would it be any different at all?

Oh and to also add I've tried this running on the jlink and stand alone and the numbers don't change.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-13 12:59 AM

TIM_PSC is unconditionally preloaded, which means, that value written to it gets taken into account only after Update event, which usually means the nearest overflow/underflow. In your latter case with changing to downcounting you've effectively caused underflow just as the timer starts to run. As TIM5 is a 32-bit timer, even at the default no prescaler it takes considerable time until it overflows for the first time, when counting up.

The usual trick is to set TIM_EGR.UG to force an Update just after writing to TIM_PSC, but note that should you enable the Update interrupt, it would fire immediately.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-13 10:34 AM

That was the magic bullet. Thank you for your help. The working code:

__HAL_RCC_TIM5_CLK_ENABLE();

TIM5->PSC = HAL_RCC_GetPCLK1Freq()/1000000 - 1;

TIM5->EGR = TIM_EGR_UG;

TIM5->CR1 |= TIM_CR1_CEN;I might search for the other thread I found I this issue and update that one too. As so often happens there was no resolution to the thread.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-24 8:50 PM

I have to update this thread.

The above code MIGHT work for other STM32 MCUs but it does NOT work for the STM32F7 in all cases:

In my case:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-25 12:01 AM

There's probably a dedicated incantation in Cube/HAL to determine the timers' clock. I don't Cube.

JW

- Stop mode on Threadx with BLE on WBA in STM32 MCUs Wireless

- STM32 AzureRTOS USBX MTP: Hierarchical folder structure not working (Folders appear empty) in STM32 MCUs Embedded software

- NUCLEO-L452RE-P current consumption way more than expected - ~ 20µA - 30µA in Shutdown Mode in STM32 MCUs Products

- I2C STM32CubeMX HAL code: Target receive in interrupt mode TransferDirection issue in STM32 MCUs Embedded software

- CubeMX 6.17.0 generates wrong code for HSE_RTC divider in STM32CubeMX (MCUs)