- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Use timer`s chain to generate N impulse`s

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Use timer`s chain to generate N impulse`s

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-24 4:05 PM

I do some serial interface clock with timers chain on stm32f407.

Thats work, but generate little bit lower count of impulses. where is my trouble? len is about 16 384, overall pulse count len*16.

I miss about 200*16=3200 pulses.

Thank You!

TIM2->PSC=0;

TIM2->ARR=3-1;//3 tact`s per pulse

TIM2->CCR2= 1;

TIM2->CCER |= (TIM_CCER_CC2E);

TIM2->CCMR1 &=~( TIM_CCMR1_OC2M_0);

TIM2->CCMR1 |= ( TIM_CCMR1_OC2M_1 | TIM_CCMR1_OC2M_2);

//TIM2 slave gate mode and source ITR3

TIM2->SMCR &= ~(TIM_SMCR_SMS_Msk | TIM_SMCR_TS_Msk);

TIM2->SMCR |= TIM_SMCR_SMS_0 | TIM_SMCR_SMS_2 | TIM_SMCR_TS_0 | TIM_SMCR_TS_1;

// TIM4 up counting mode, pulse width to TRGO

// Prescaler = 3_tact`s_per_pulse * 16_bits_per_Word -1

TIM4->PSC = 3*16 -1;

TIM4->ARR = len;

TIM4->CR1 &= ~(TIM_CR1_ARPE_Msk | TIM_CR1_CKD_Msk | TIM_CR1_CMS_Msk | TIM_CR1_DIR_Msk);

TIM4->CR1 |= TIM_CR1_OPM ;

TIM4->CR2 &= ~(TIM_CR2_CCDS_Msk | TIM_CR2_MMS_Msk | TIM_CR2_TI1S_Msk);

TIM4->CR2 |= TIM_CR2_MMS_0;

//reset counters

TIM4->EGR |= TIM_EGR_UG;

TIM2->CR1 |= TIM_CR1_CEN;

TIM4->CR1 |= TIM_CR1_CEN;

while (TIM4->CR1 & TIM_CR1_CEN){

cntr++;

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-24 4:23 PM

Maybe is there another way to do that!?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-24 5:22 PM

What is your timer clock speed and how are you measuring pulses? By my count, you are generating 262160 pulses. Switching PWM output every 1-2 cycles might produce a signal without a very good edge.

Might be easier to diagnose if you reduced the number of pulses to something easily viewed on a scope. Say 8. Then, once that's working, scale up to what you really want.

You probably want "TIM4->ARR = len -1;" but that couldn't be the issue.

Could use SPI_SCK to output pulses but only if it fits with your clock.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-24 5:28 PM

Thank You For Interest!

I found if len below than 208 no impulses. correct count of impulses generated if use len+208

168 MHz CPu, 84 MHz AHB2, 84/3 to out, its work stable, but what is 208?

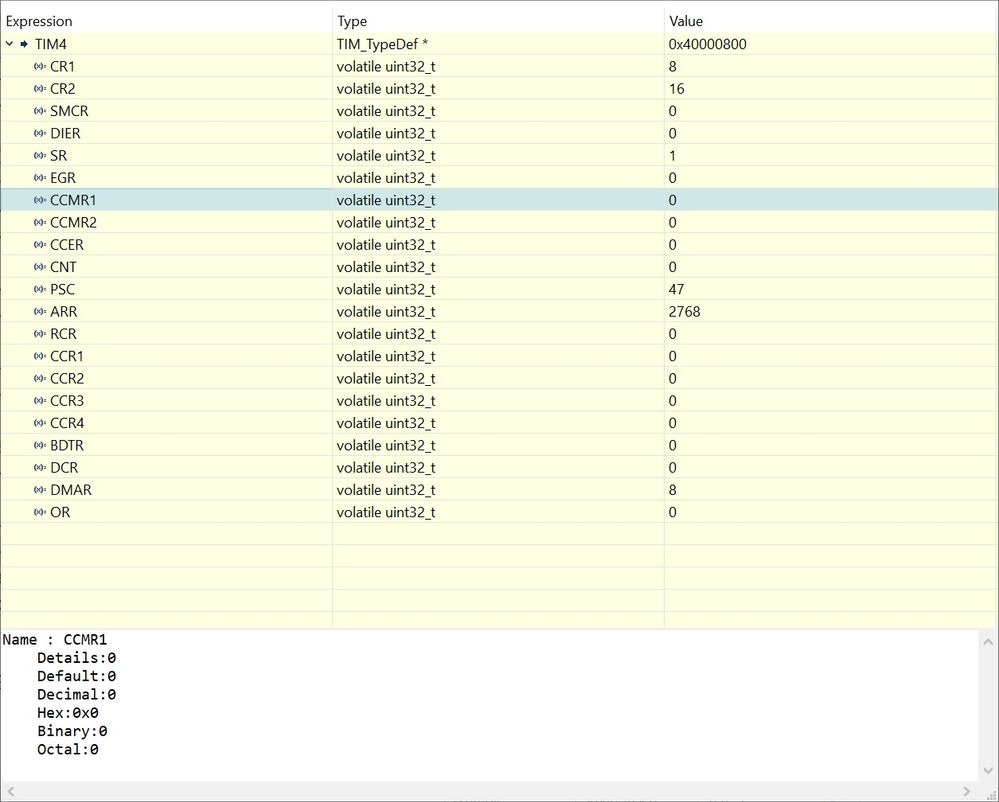

timer state before start with

TIM4->ARR = 128*20+208;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-24 5:31 PM

Set TIM4->CNT to 0 before you start it. It could be starting from a higher value, which would mess up the number of pulses you get.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-24 5:42 PM

Thank You! But no Effect.

Thank You!!! It`s need to reset slave timer parameters.

TIM2->EGR |= TIM_EGR_UG;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-24 5:44 PM

Interface is very close to SPI, but data maybe 6-19 bit per pixel.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-24 6:30 PM

//RESULT CODE. Thanks for ALL!

TIM2->CR1 |= TIM_CR1_ARPE;

TIM2->PSC=0;

TIM2->ARR=3-1;//3 tact`s per pulse

TIM2->CCR2= 1;//pulse width 2 of 3

TIM2->CCER |= (TIM_CCER_CC2E);

TIM2->CCMR1 &=~( TIM_CCMR1_OC2M_0);

TIM2->CCMR1 |= ( TIM_CCMR1_OC2M_1 | TIM_CCMR1_OC2M_2);

TIM2->SMCR &= ~(TIM_SMCR_SMS_Msk | TIM_SMCR_TS_Msk);

//TIM2 slave gate mode and source ITR3

TIM2->SMCR |= TIM_SMCR_SMS_0 | TIM_SMCR_SMS_2 | TIM_SMCR_TS_0 | TIM_SMCR_TS_1;

// TIM4 up counting mode, pulse width to TRGO

// Prescaler = 3_tact`s_per_pulse * 16_bits_per_Word -1

TIM4->CNT = 0;

TIM4->PSC = 3*16 -1;

TIM4->ARR = len;

TIM4->CR1 &= ~(TIM_CR1_ARPE_Msk | TIM_CR1_CKD_Msk | TIM_CR1_CMS_Msk | TIM_CR1_DIR_Msk);

TIM4->CR1 |= TIM_CR1_OPM ;

TIM4->CR2 &= ~(TIM_CR2_CCDS_Msk | TIM_CR2_MMS_Msk | TIM_CR2_TI1S_Msk);

//CNT_EN of TIM4 is used as TRGO

TIM4->CR2 |= TIM_CR2_MMS_0;

//reset counters

TIM4->EGR |= TIM_EGR_UG;

TIM4->SR &= ~ TIM_SR_UIF_Msk;

TIM2->EGR |= TIM_EGR_UG;

TIM2->SR &= ~ TIM_SR_UIF_Msk;

TIM2->CR1 |= TIM_CR1_CEN;

TIM4->CR1 |= TIM_CR1_CEN;

while (TIM4->CR1 & TIM_CR1_CEN){ cntr++; }

- Is there a board where I generate 4 different PWM signals at the same time? in STM32 MCUs Boards and hardware tools

- STM32H755 HR timer synchronization with general purpose timers in STM32 MCUs Products

- STM32H7: possible to configure HRTIM1 TIMA to trigger TIM13 start without SW ISR? in STM32 MCUs Products

- CubeIDE issue with timers in STM32CubeIDE (MCUs)

- TIM Trigger DMA in STM32CubeMX (MCUs)