- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: There is a 5.6V peak on the rising edge using ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

There is a 5.6V peak on the rising edge using STM32F103 TIM1 PWM output pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-06-14 11:18 PM

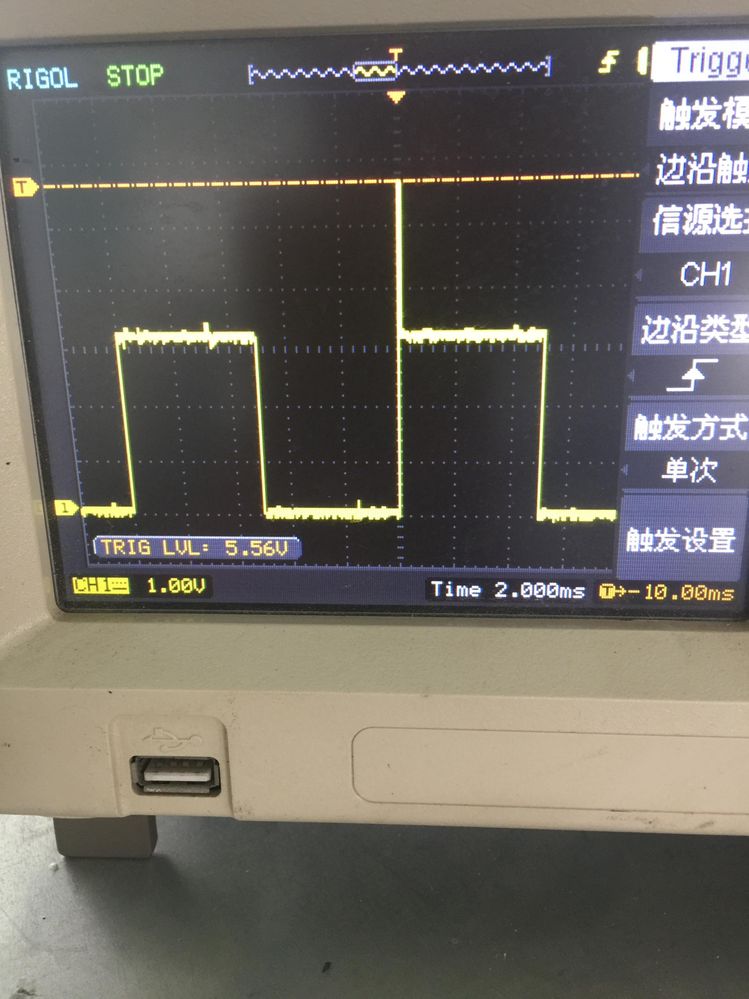

Hi everybody!Recently I found a strange phenomenon that there was a peak on the rising edge when I using the TIM1's 4 chanels to be PWM output mode.And the maxium peak voltage can reach to 5.6V measured by the oscilloscope.But the maxium voltage supplied for the MCU was just 3.45V measured by the same oscilloscope.

So where was the 5.6V peak voltage from?Please help me!

Environment:

1.MCU model:STM32F103VET6

2.Core clock:72MHZ

3.Used TIMER:TIM1

4.Timer Mode:PWM output mode

5.PWM frequency:100Hz

6.Duty cycle:50%

7.PWM driver load:No load

8.PWM output pin configuration:GPIO_Output_AF_PP

#stm32-pwm

#stm32-pwm

- Labels:

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-06-15 01:29 AM

Inductive load?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-06-15 05:06 AM

Or another artifact, related to scope / probe impedance.

Otherwise, it would be persistent (with every rising edge).

Does it disappear when you zoom in (record with higher sampling rate) ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-06-15 05:27 AM

Thank you for replying.I have tried zoom in or changing the probe impedance but the peak always exited.And I measured 3 different board with differrent cicurt,the phonomenon exits always.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-06-15 05:29 AM

I measured the wave when the PWM pin was not connected to any load.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-06-15 06:17 AM

You may check the voltage by a DMM first, is it 2.8V (suppose really 5.6V square wave).

I had been fooled by xx-Instek oscilloscope's certain malfunctioning channel.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-06-15 07:50 AM

Are you certain you are making a 'single ended' measurement with a common 0V between your circuit and the oscilloscope?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-06-15 08:05 AM

Is there >3.3V on any other pin of the mcu?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-06-15 08:59 AM

Select less aggressive slew rate (IO Speed), ie use the 1 or 2 MHz settings, not the 50 or 100 MHz ones

Poor grounding, pretty sure it's not coming from the STM32F1 inherently. Plot the VDD vs VSS on the second channel of the scope.

Up vote any posts that you find helpful, it shows what's working..

- STM32H753 QSPI Status Flag Polling fails with Instruction on 4 lines in STM32 MCUs Products

- How to correctly dimension an external pullup resistor in Low Power application in STM32 MCUs Wireless

- Floating outputs when not connected to PWM Timer 8 in STM32 MCUs Products

- STM32H7 SPI flash fast read timing calculation in STM32 MCUs Products

- STM32H7R3 PSSI RDY/DE bug in STM32 MCUs Products