- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- System clock configuration using register level pr...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

System clock configuration using register level program.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-17 1:37 AM

We are working on an existing project, in which our microcontroller's flash size was exceeding the value of our code size. So we decided to move to a register level program.

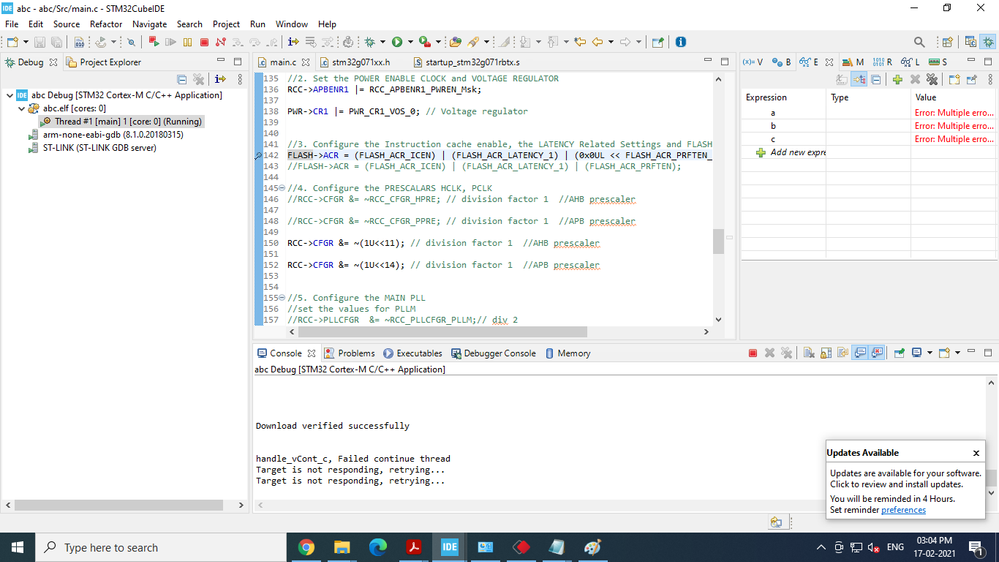

We did system clock configuration at 64 MHz, while debugging after step no 3 (Configure the Instruction cache enable, the LATENCY Related Settings and FLASH PREFETCH), the debugging shuts down. Here is the attached code and the error.

int main(void)

{

int a;

int b;

int c;

SystemClock_Config(); // SystemClock_Config() commented

/* Loop forever */

while(1)

{

a=5;

b=2;

c=a+b;

c=a*b;

}

}

void SystemClock_Config(void)

{

/*************>>>>>>> STEPS FOLLOWED <<<<<<<<************

1. ENABLE HSI and wait for the HSE to become Ready

2. Set the POWER ENABLE CLOCK and VOLTAGE REGULATOR

3. Configure the FLASH PREFETCH and the LATENCY Related Settings

4. Configure the PRESCALARS HCLK, PCLK1, PCLK2

5. Configure the MAIN PLL

6. Enable the PLL and wait for it to become ready

7. Select the Clock Source and wait for it to be set

********************************************************/

//1. ENABLE HSI and wait for the HSI to become Ready

RCC->CR |= RCC_CR_HSION;

while(!(RCC->CR & RCC_CR_HSIRDY));

//2. Set the POWER ENABLE CLOCK and VOLTAGE REGULATOR

RCC->APBENR1 |= RCC_APBENR1_PWREN_Msk;

PWR->CR1 |= PWR_CR1_VOS_0; // Voltage regulator

//3. Configure the Instruction cache enable, the LATENCY Related Settings and FLASH PREFETCH.

FLASH->ACR = (FLASH_ACR_ICEN) | (FLASH_ACR_LATENCY_1) | (0x0UL << FLASH_ACR_PRFTEN_Pos);

//FLASH->ACR = (FLASH_ACR_ICEN) | (FLASH_ACR_LATENCY_1) | (FLASH_ACR_PRFTEN);

//4. Configure the PRESCALARS HCLK, PCLK

//RCC->CFGR &= ~RCC_CFGR_HPRE; // division factor 1 //AHB prescaler

//RCC->CFGR &= ~RCC_CFGR_PPRE; // division factor 1 //APB prescaler

RCC->CFGR &= ~(1U<<11); // division factor 1 //AHB prescaler

RCC->CFGR &= ~(1U<<14); // division factor 1 //APB prescaler

//5. Configure the MAIN PLL

//set the values for PLLM

//RCC->PLLCFGR &= ~RCC_PLLCFGR_PLLM;// div 2

//set the values for PLLN

//RCC->PLLCFGR |= RCC_PLLCFGR_PLLN_3;// X 8

//set the values for PLLR

//RCC->PLLCFGR |= RCC_PLLCFGR_PLLR_0;// / 2

//PLL input clock source

//RCC->PLLCFGR |= RCC_PLLCFGR_PLLSRC_HSI;

#define PLL_M 1

#define PLL_N 8

#define PLL_R 2 // PLLP = 2

//#define PLL_Q 2 // PLLP = 2

//#define PLL_P 2 // PLLP = 2

RCC->PLLCFGR = (PLL_M <<4) | (PLL_N << 8) | (PLL_R <<29) | (2<<0);

//RCC->PLLCFGR = (PLL_M <<4) | (PLL_N << 8) | (PLL_R <<29) | (2<<0) | (PLL_Q<<25) | (PLL_P<<17);

//6. Enable the PLL and wait for it to become ready

RCC->CR |= RCC_CR_PLLON;

while(!(RCC->CR & RCC_CR_PLLRDY));

//7. Select the Clock Source and wait for it to be set

RCC->CFGR |= RCC_CFGR_SW_1; //System clock switch PLLRCLK

while(!(RCC->CFGR & RCC_CFGR_SWS_1));

}

Let me know if there's an alternative solution to this issue.

- Labels:

-

Flash

-

STM32G0 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-17 4:27 AM

Each device/architecture supports a limited amount of HW breakpoints - on silicon.

Many toolchains offer additional SW breakpoints (managed by the debugger), but not for free.

> We are working on an existing project, in which our microcontroller's flash size was exceeding the value of our code size.

The Cube compiler is average at best when it comes to code size.

Have you tried optimisation for size ?

Check the map file, and find the worst offenders, i.e. the objects occupying the most Flash space.

Starting with the clock configuration and similar low-level / IO-heavy functions seems not the most effective approach to me.

Have you considered a better toolchain, like Keil uVision or IAR WB ?

Not only offer they better debug support (see above), but more important, far better optimisation.

At average, you get what you pay for.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-17 5:55 AM

Dear Sir,

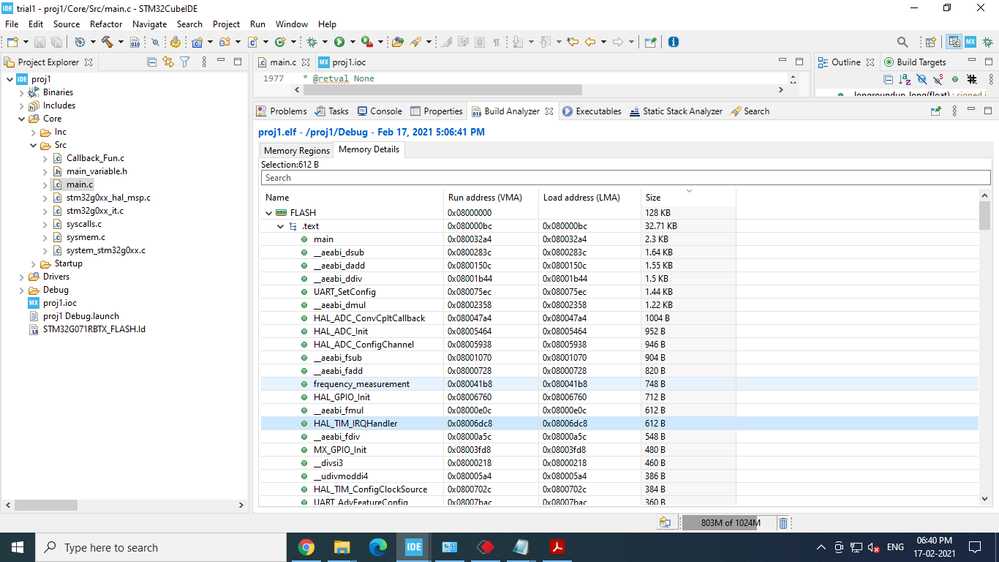

- First things is we are developing low cost product. and HAL and LL driver took more memory than we decided for our product controller and we also tried code optimization. so have to go compulsory on register level programming here I attached memory_details picture.

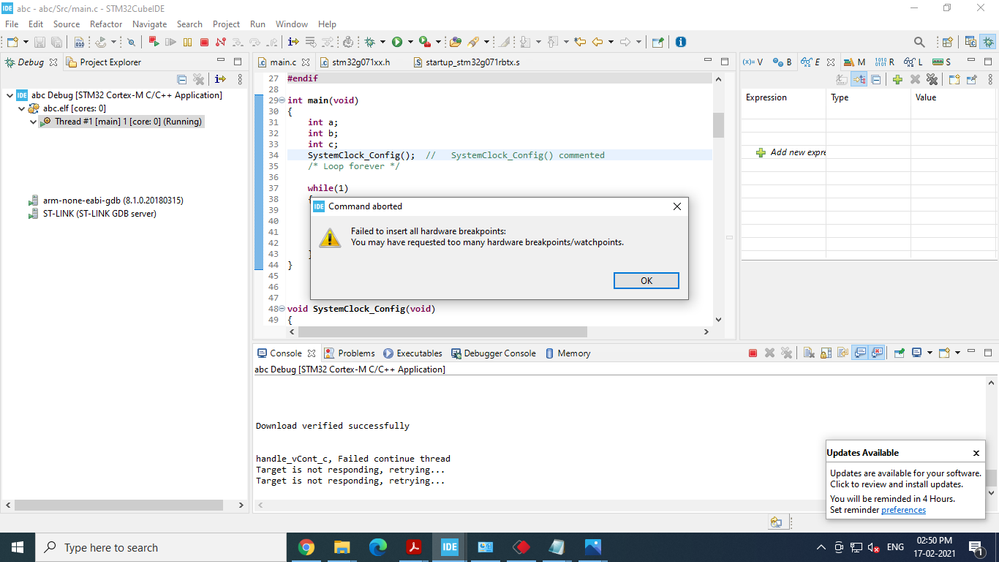

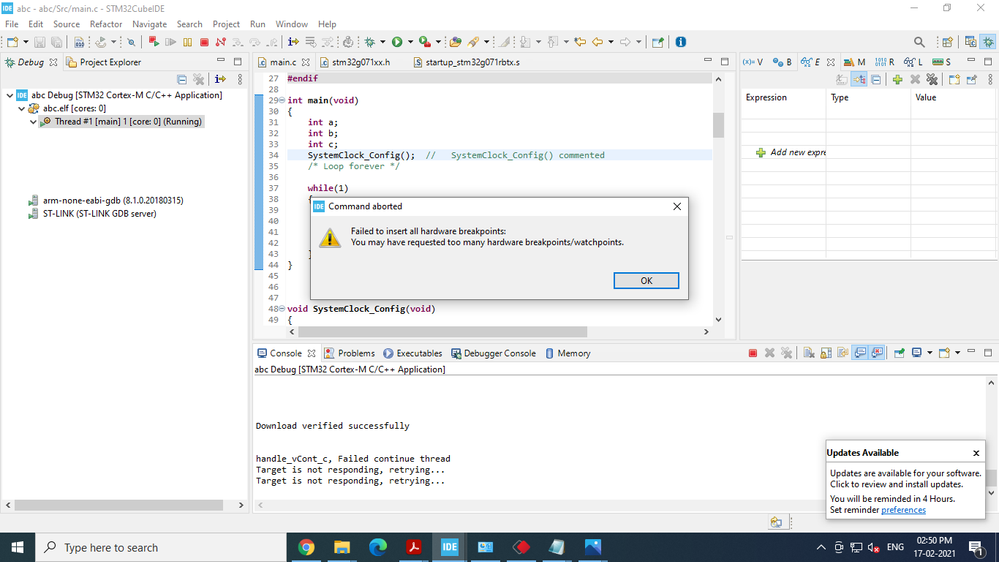

- Second things was we did debug without breakpoint then also error message occurred. here I attached debug_withoutBreakpoint picture.

Let me know if there is another solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-17 6:17 AM

Check what clock you're actually running from at the point where you fiddle with the ACR.

Which clock does the STM32G071 run from at startup?

Does the code in SystemInit() set things up?

Make sure the code isn't pulling the entire float library in to do baud rate computations.

Perhaps consider assembler.

Up vote any posts that you find helpful, it shows what's working..

- STM32F407VET6 Black Pill V2 in STM32 MCUs Embedded software

- HELP with Burst Mode HRTIM in STM32 MCUs Boards and hardware tools

- What is the best PLL configuration for H533 ? in STM32 MCUs Products

- Problem with StmcubeIDE 2.0.0 in STM32CubeIDE (MCUs)

- STM32F407G-DISC1 code fails to draw a rectangle on ILI9341 screen in STM32 MCUs Boards and hardware tools