- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32H7 reading QUADSPI->DR freezes the MCU after ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H7 reading QUADSPI->DR freezes the MCU after QUADSPI->CCR = QUADSPI_CCR_FMODE_0 | QUADSPI_CCR_IMODE_0;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-02 1:36 AM

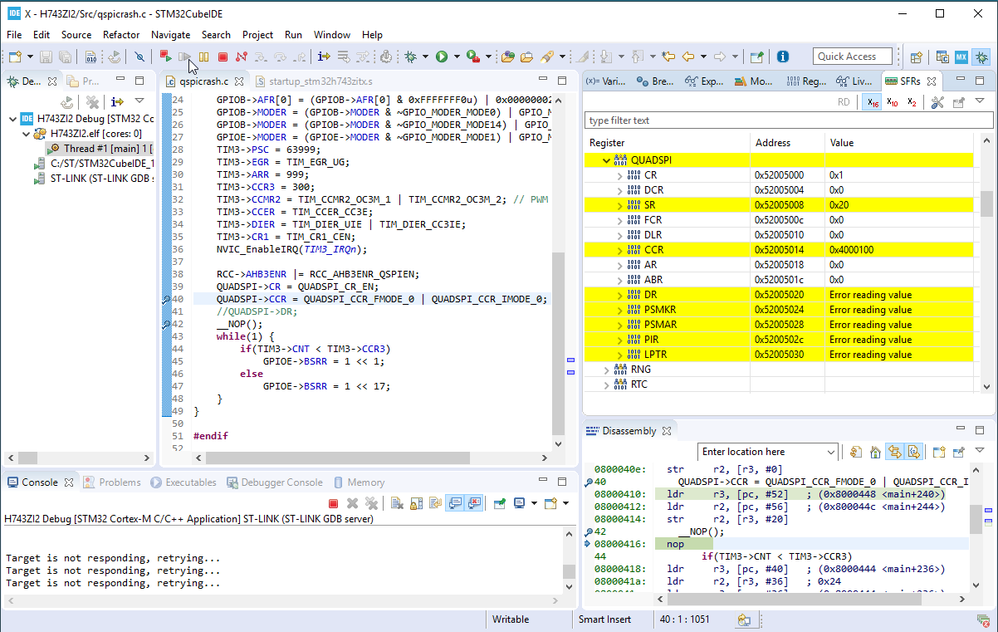

Executing this code sequence on a STM32H743ZI or STM32H743II

RCC->AHB3ENR |= RCC_AHB3ENR_QSPIEN;

QUADSPI->CR = QUADSPI_CR_EN;

QUADSPI->CCR = QUADSPI_CCR_FMODE_0 | QUADSPI_CCR_IMODE_0;

QUADSPI->DR;i.e. indirect read with only an instruction phase, then reading the data register freezes the MCU, i.e. no further instructions are apparently executed.

Debugger connection is lost, tries to reconnect a couple of times then gives up. I was able to reconnect the debugger only with Connect under reset enabled.

Watching the QSPI registers in the debugger has the same effect even when the DR register is not directly read by the code.

Workaround: avoid this sequence, use indirect write mode instead to send SPI commands with no parameters.

UPDATE

I have read the reference manual (better late than never) and found this:

When DMODE = 00, the data phase is skipped, and the command sequence finishes immediately by raising nCS. This configuration must only be used in only indirect write mode.

... and I was using DMODE = 00 in indirect read.

Solved! Go to Solution.

- Labels:

-

Bug-report

-

QSPI

-

STM32H7 series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-03 5:47 AM

@berendi

Which device do you communicate with ? this detail is important , to check if QSPI is properly configured in this case.

You must insert at least one dummy cycle. Following the RM0433 page 886 , section Dummy-cycle phase : "In order to assure enough “turn-around�? time for changing the data signals from output mode to input mode, there must be at least one dummy cycle when using dual or quad mode to receive data from the Flash memory. "

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-03 6:58 AM

Hi @Imen DAHMEN ,

The error occurs regardless of whether there is any device connected or not. When there is, it is a Winbond W25Q128JV-DTR, or a pair of them, which otherwise work(s) well at 133 MHz on a custom board. I've tried with lower speeds as well, no change.

Never mind, I've found the relevant note in the last paragraph of the Data phase section.

When DMODE = 00, the data phase is skipped, and the command sequence finishes immediately by raising nCS. This configuration must only be used in only indirect write mode.

... and I was using DMODE = 00 in indirect read. Sorry for the confusion.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-03 7:07 AM

@berendi Glad to know that your issue is solved :smiling_face_with_smiling_eyes:

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-03 8:40 AM

A combination of settings which can stall the processor indefinitely and unrecoverably is IMO a condition worth explicit mention in the RM.

Interestingly, the same sentence for DMODE = 00 is in RM0351, yet you've said 'L4 is unaffected...

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-10 1:00 PM

@Imen DAHMEN

Similar problem here:

using STM32F769-EVAL, QSPI indirect mode , no device attached. The goal is to use the QSPI to read from FPGA so all is need is a simple 4 lines SPI. Just data phase. Each time it will be either read or write so the system doesn't require any dummy cycles.

the read is performed by : status=HAL_QSPI_Receive_DMA(&hqspi,buffer);

DLR is set to 63 (reading 64bytes each time)

the command is executed (verified using scope)

The problem: sometimes the busy bit clears and sometimes not.

DMA is in use, is there a need to do anything else?

Doesn't the DMA mechanism clear the FiFo thus clearing busy bit?

thanks,

Arnon

- « Previous

-

- 1

- 2

- Next »