- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32G431KB strange DAC slew rate behaviour

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32G431KB strange DAC slew rate behaviour

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-07 4:46 PM

I assume this issue applies to DACs across all the MCUs but I am testing on a Nucleo-G431KB so I'll stick with the scientific facts.

When I write a 12bit DAC value greater than 4060, the "down" slew rate in buffered output mode drops off a cliff.

For values between 0 and 4060 the up and down slew rates are symmetrical.

My assumption is that the analog output buffer is adding a slew issue due to latching up near the supply rails but the docs don't seem to mention this.

Aside from limiting the DAC output range or moving to an external buffer (which for parts count reasons would be nice to avoid), has anyone else experienced this or has an insight into why it happens?

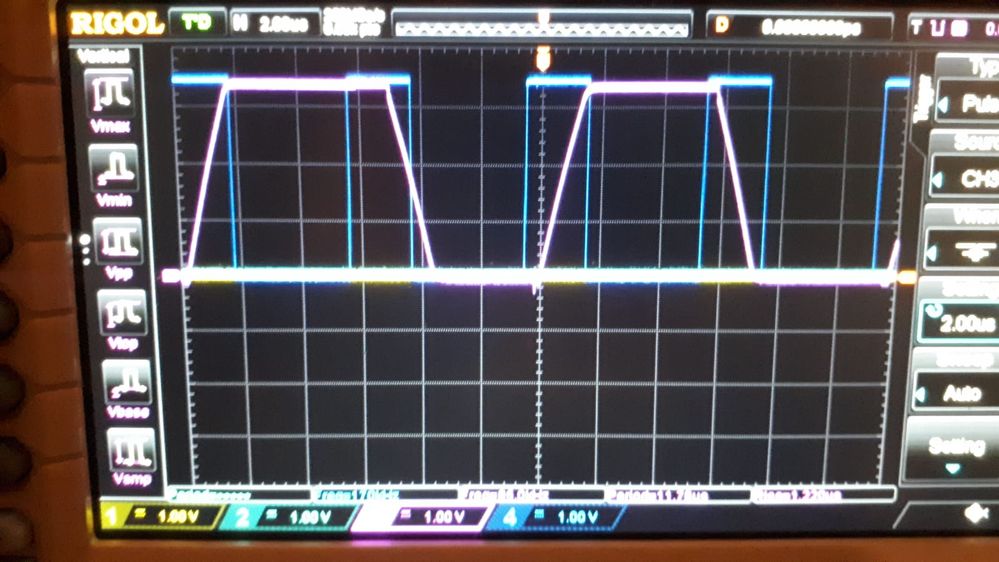

The below image has the DAC going from 0 to 4095 then 0 to 4060.

See how the "down" section is quite slow from 4095 to 0, but fast from 4060 to 0.

The blue waveform is a timing reference from a PWM on the same timer driving the DAC:

- Labels:

-

DAC

-

STM32G4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-09 4:04 AM

What is your VDDA and VREF? If both are the same, the buffering OP might be in saturation, where recovery takes some time. Try with e.g. VDDA = 3.3V and VREF 3.0 V to have some margin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-09 5:37 AM

Hello,

As you are using output buffer, the output voltage is limited at 0.2V to VREF+-0.2V

If output buffer is saturated, as output buffer is opamp structure, it's feedback is not correctly closed. then output voltage goes down it needs some time to be correctly biased. So if you would like to use buffered mode with correct beahvioue, please use between 0.2V to VREF+-0.2V.

Regards

Kenichi

- STM32G474 pin PB4 stays high for 27ms approx, After reset and before making it low as GPIO in STM32 MCUs Products

- L073 strange behaviour after 2nd bootloader jump to app in STM32 MCUs Products

- Strange CRC behaviour in STM32 MCUs Products

- H723..H735: functions in ITCM, strange behaviour in STM32 MCUs Products

- LiveWatch causes breakpoints to still be active after debugger stops in STM32CubeIDE for Visual Studio Code (MCUs)