- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32F437IIH6 ECC and NAND Flash size

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F437IIH6 ECC and NAND Flash size

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-15 4:14 AM

Hello.

1. Whether the hardware ECC for STM32F437IIH6 support error detection and error correction? STM32F437 is connect to NAND Flash through FMC with Bank2. Reference manual RM0090 section 37.6.6 describe it can perform 1-bit error correction and 2-bit error detection. This error detection and error corretion is supported by hardware or realized by software?

2.Figure 457 FMC memory banks in RM0090 describe the Bank2 for NAND Flash is 4x64 MB. Is that means the NAND flash connected to Bank2 should be 256MB max.? However, as NAND flash doesn't have address pins, and the address is defined through the commands, whether I can connect a 512Mbytes or 1Gbytes NAND Flash to Bank2?

Thank you.

Solved! Go to Solution.

- Labels:

-

FMC-FSMC

-

STM32F4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-22 3:56 AM

There isn't a size limit as the memory is not entirely mapped, but rather acts as a block storage device.

The STM32 does not do correction, that must be done in software. The hardware was able to do some generation and checking functionality, but that is typically done by the NAND memories themselves these days based on the geometry and level requirements.

The industry has generally migrated to eMMC at this point as this manages most of the ugliness of managing blocks, wear, ECC, etc of NAND Flash using a common footprint and SDIO/SDMMC interface. Should support 100's of GB with no problems.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-16 2:41 AM

Hello, is there anybody could help on this? Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-22 1:44 AM

It's a pity to say that ST community seems not friendly or helpful for developer/engineers. When I ask a question in TI or Microchip community, I can get the response in few hours, that's efficient and surprised to me. However, in here the ST community, 1 week have past but nobody answer my question.

Please try to have a feedback to help on this . Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-22 3:56 AM

There isn't a size limit as the memory is not entirely mapped, but rather acts as a block storage device.

The STM32 does not do correction, that must be done in software. The hardware was able to do some generation and checking functionality, but that is typically done by the NAND memories themselves these days based on the geometry and level requirements.

The industry has generally migrated to eMMC at this point as this manages most of the ugliness of managing blocks, wear, ECC, etc of NAND Flash using a common footprint and SDIO/SDMMC interface. Should support 100's of GB with no problems.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-22 6:49 PM

Hello DeLorean,

Thank you for your comments.

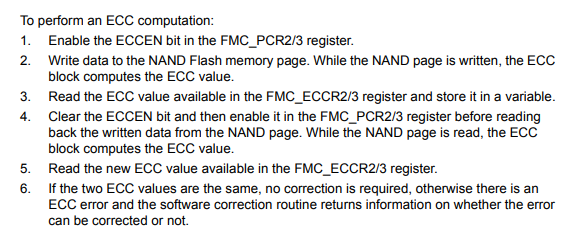

For the FMC ECC, the reference manual RM0090 page1653 says "The FMC PC Card controller includes two error correction code computation hardware

blocks, one per memory bank. They reduce the host CPU workload when processing the ECC by software.", "The ECC algorithm implemented in the FMC can perform 1-bit error correction and 2-bit error detection". Those not mean the support of hardware ECC for error correction and detection? Or actually FMC is doing the calculation/computation of the error correction code by hardware, and the correction action is finally implemented by software? Whether the main part which takes CPU workload is calculation error correction code, not the correction action?

For the eMMC, Yes it is very convenient to be used, however, the eMMC (usually MLC NAND eMMC) is typically about 3000 program/erase cycles, however SLC NAND flash can up to 100000 program/erase cycles. As we are doing medical devices and the device life cycle shall be 10 years. So eMMC seems not a good choice for us.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-22 10:59 PM

As I understand the mechanics of the HW it does the laborious bit level stuff, allowing you to generate the ECC codewords that can be appended, or drop out the error syndromes so you can work out and fix the offending bits/bytes in the RAM copies you've pulled.

Last time I got deep into NAND memories, the newer architectures had the logic to do much the same thing, using algorithms the manufacturer determined most appropriate for the characteristics and failure mechanisms of the cells. This deprecates the usefulness of the ST implementation, and basically why it was dropped from subsequent families, and isn't particularly well documented or supported. At one time they had libraries and demo boards, but then they spun out the NAND group.

Unfortunately I'm not that interested in working on this ECC HW, and I expect the audience is pretty limited.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-22 11:23 PM

Hello DeLorean,

Thanks for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-26 9:46 AM

Hello @WLiao.1,

Let me first welcome you to the STM32 Community :smiling_face_with_smiling_eyes: and sorry for the delay to reply you.

I just looked at my actions and realized that I had not responded to your post.

Thanks @Community member for your help and clarification on this post =)

I will add some notes:

1-It is error detection and possible 1-bit correction, done by CPU and only the ECC computation is done by hardware. In the RM, there is an example use case.

2- In the RM0090 (page 1648) , you will find this note:

Imen

Thanks

Imen

- LSM6DSO I3C SETDASA in STM32 MCUs Embedded software

- ST-LINKV3 over VirtualHere (USB over IP) in STM32 MCUs Products

- STM32CubeMX with MMT: strange LD file generation in STM32CubeMX (MCUs)

- STM32H573 Secure partition starts at 0xc000400 or 0xc000000? Mapping differs from OBkey settings in STM32 MCUs Security

- About BOOT0 and BOOT1 pins on STM32G474R ? in STM32 MCUs Products