- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F413 DMA1 peripheral restrictions?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F413 DMA1 peripheral restrictions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-18 10:29 AM

I'm having trouble understanding this from the datasheet and reference.

What peripherals are allowable targets for DMA1 memory-to-peripheral transfers?

Thanks, Best Regards, Dave

PS: I tried to use a stream in DMA1 to write to a DMA control register, and it fails...

Solved! Go to Solution.

- Labels:

-

DMA

-

STM32F4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-18 11:17 AM

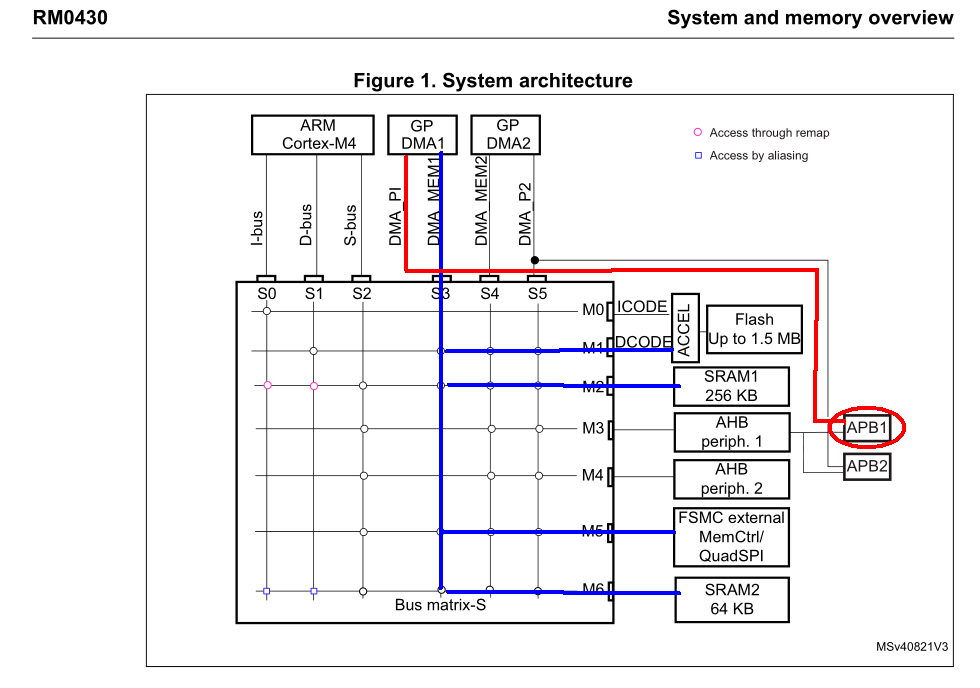

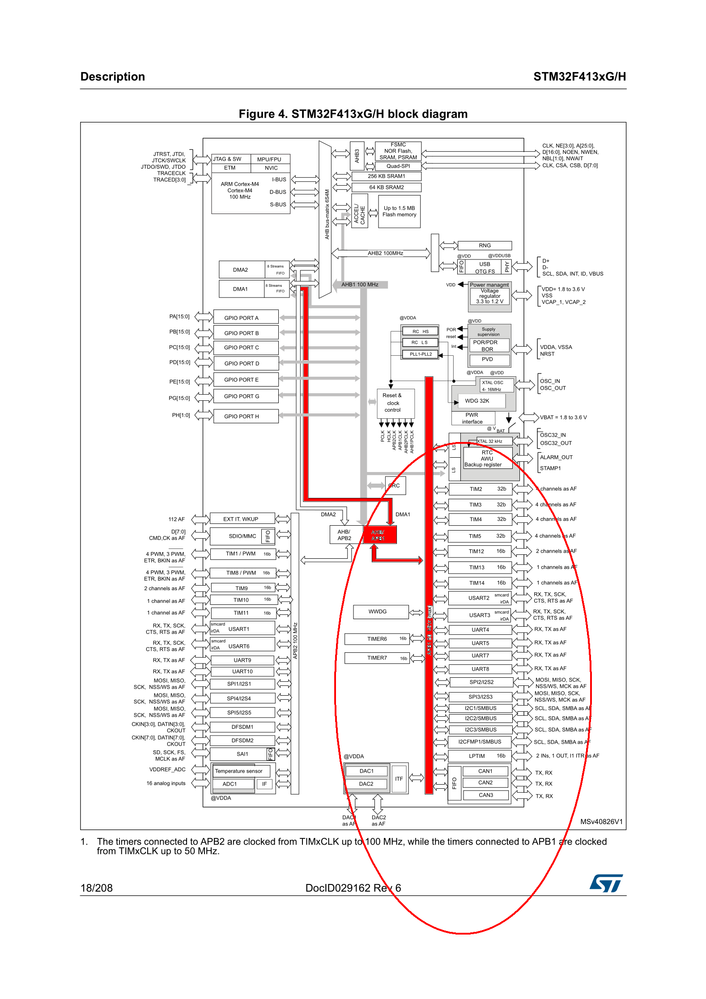

Oh, of course not. This is the picture you are looking for:

and this one:

(There's also Tab.1 in RM, but that's way less sexy).

However, except for timer, I don't recommend you to use any other peripheral-port target than the data register of the peripheral which triggers that stream. And note, that on the memory port you can't access peripherals (not even APB1 peripherals), only memories. So, for most practical purposes, the table given by md.suhel is adequate.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-18 10:39 AM

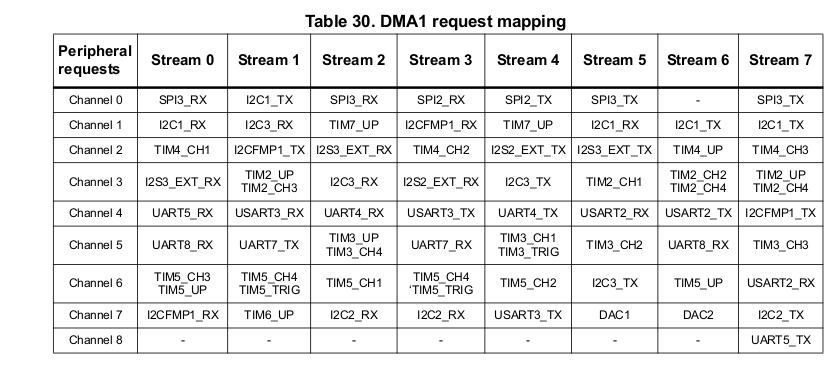

Below table from the reference manual should provide you the information you are looking for.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-18 10:48 AM

The question posed is: What are the restrictions on peripheral targets (ie, peripherals that can be written to) for DMA1?

The posted table shows DMA request channels; not what I asking about...

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-18 11:17 AM

Oh, of course not. This is the picture you are looking for:

and this one:

(There's also Tab.1 in RM, but that's way less sexy).

However, except for timer, I don't recommend you to use any other peripheral-port target than the data register of the peripheral which triggers that stream. And note, that on the memory port you can't access peripherals (not even APB1 peripherals), only memories. So, for most practical purposes, the table given by md.suhel is adequate.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-18 11:43 AM

>>What peripherals are allowable targets for DMA1...

APB1 targets

DMA2 can do memory-to-memory, so APB2 targets, plus anything else, ie GPIOB->ODR

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-18 12:21 PM

Thanks @Community member - I saw that but I've confused about the nomenclature. In the datasheet there's a memory table that shows the following. AHB1 vs. APB1? What I'm missing is which peripherals are associated with APB1? Aha! Thanks @Community member for pointing me to the diagram and table.

Appreciate the help!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-18 12:28 PM

And I now see why my DMA failed. I'll need to rework the puzzle to get a trigger into some DMA2 stream (perhaps by chaining timers)... Thanks Guys!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-18 12:53 PM

> What I'm missing is which peripherals are associated with APB1?

Those in the red circle in that second picture I posted above.

And, as I've said there, in Tab1 in RM they are listed, with APB1 in the column next to them. (those which have AHB1 in that column, belong to... ehm... AHB1; similar with other buses).

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-19 12:31 AM

There are 2 DMA stream/channel tables. You can choose one element per column.

What is in the box is the DMA incoming memory request trigger signal source.

If it is SPI_TX, means it's for the memory to peripheral transfer.

Find in which table the peripheral you'd like to use is located.

One DMA per clock domain...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-02 2:31 AM

On this note there is an error in Table 30. DMA1 Request Mapping:

Channel 5 Stream 0, should be UART8_TX (Not Rx)

- The callback function HAL_DAC_ConvCpltCallbackCh1(DAC_HandleTypeDef* hdac) with STM32U575CGU6 doesn't work in STM32 MCUs Embedded software

- Why does adding a fourth module stops the firmware working as required? in STM32 MCUs Products

- Switching a project from a STM32F413 to a STM32F405 doesn't allow for debugging. in STM32 MCUs Products

- AUDIO RECORD - MEMS > DFSDM > I2S > FATFS > Ethernet in STM32 MCUs Embedded software

- Why does the DMA gets out of sync when doing a sequence of regular AD conversions on stm32f103C8TX? This only happens with DMA_NORMAL. in STM32 MCUs Products