- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F407 FSMC physical addressing

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F407 FSMC physical addressing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-04 03:56 AM

Hello everybody,

I am a new ARM microcontroller user.

I drive a winstar 3,5' display (SSD1963 embedded) with a STM32F4-discovery board.

I use FSMC to drive the display with 8080 mode.

To drive the input D/C# (Data / Command) I use FSMC address A19 (PE3).

It works fine if i use the code below :

#define LCD_REG (*((volatile unsigned short *) 0x60000000)) /* DC = 0 */

#define LCD_RAM (*((volatile unsigned short *) 0x60100000)) /* DC = 1 */The questions are:

- Why I need to write '1' to bit #20 to switch A19 to '1' ?

- Why I cannot use bit #19 rather than bit #20 ?

Thanks in advance

Regards

BP

#stm32f407-fsmc-physical-addressing Note: this post was migrated and contained many threaded conversations, some content may be missing.- Labels:

-

FMC-FSMC

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-05 07:19 AM

Hello everybody,

No answer since yesterday ... ?

I can add precision :

- To write data to the display, I write bytes at address 0x60100000 to switch D/C display input to '1'.

(Input D/C is connected to PE3 = FSMC A19)

Why I need to use the software code address 0x60100000 to switch A19 to '1' rather than address 0x60080000 ?

What is this mistery ?It seems that FSMC A0 equal to 0x60000002 rather than 0x60000001 !!!Thanks in advanceRegards

BP

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-05 08:30 AM

>>

No answer since yesterday ... ?

Some people are on vacation.

>>

What is this mistery ?

With a 16-bit bus the external address bus shifts, as A0 is not needed, it becomes a byte lane selection. Therefore A1 from the core's perspective is Pin A0 at the external interface. It's one of those mysteries debunked in the manual.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-05 10:08 AM

Hi Clive,

Thank you very much for your answer.

I am a 8 bit microcontroller user !

I suspected that 'the mystery' had to be on the 16-bit bus side

...Of course, I have read that STM32 used a 16-bit external address bus, but I've not understand the information in the Reference manual (RM0090).

Of course, I've read before to ask my question the chapter 36 Flexible static memory controller (FSMC)

It's written :

The requested AHB transaction data size can be 8-, 16- or 32-bit wide whereas the

accessed external device has a fixed data width.......And there are 2 lines, NBL[1:0], for the byte lane selection.

It's not clearly written that A1 from the core's perspective is Pin A0 at the external interface.

So again, Thank you for your answer

B.PICARD

PS : Sorry for my poor english writing... I'm French !

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-05 04:41 PM

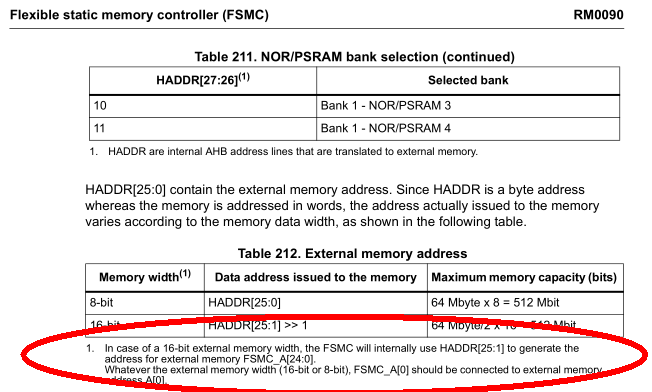

I believe it may be not entirely clear especially for those who don't have much experience with 16/32-bit buses interfacing, but the following remark is relevant to the case (an older v11 of RM0090, but I believe the current v15 has it in the same way):

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-07 07:15 AM

Hi JW,

Thank you very much for your anwer.

OK I've read too quickly the chapter and I've missed this important remark !

The remark is written in section 36.4.1 table 213 inside RM0090 rev. 14 manual dated of april 2017

I don't know why this section (36.4.1) is named NOR/PSRAM rather than NOR/PSRAM/SRAM...

Have a nice WE

BP

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-23 08:28 AM

Hi JW,

I'm using the FMC bus on a STM32F7 for an SRAM in 32-bit width.

In the RM there is the same mark, that FMC_A[0] should be connected to A[0] from external memory. My problem is now I should address the external SRAM in byte-address mode, bit with this address-shifting, it is a 32-bit-address mode.

Therefore I should connect FMC_A[2] to A[0] from external memory. Is this correct?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-23 08:42 AM

No. As said above, you always connect A0 to A0.

16- and 32-bit memories have ''byte write'' pins (2 in case of 16-, and 4 in case of 32-bit) - if you want bytewise access, you connect them to FMC_NBLn pins of STM32.

FMC, based on FMC_BCR.MWID setting for 16/32-bit memory then decodes the lower 1/2 internal address into the 2/4 NBLn bits, and shifts the internal register by those 1/2 bits to the right before outputting to pins.

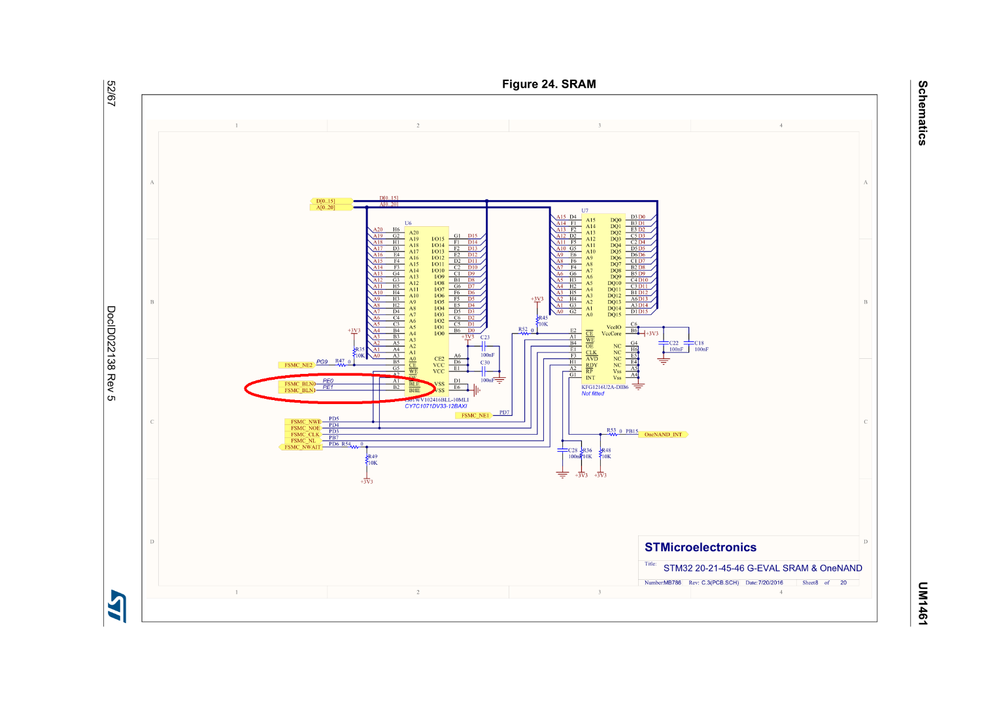

For example, this is a 16-bit SRAM as used on an EVAL board:

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-27 07:55 AM

Hi JW,

In my project I need address lines A15-A0 for my external memory. The databus is 32-bits width. This memory is shared with another microprocessor to exchange data between my STM32 and the other processor and the memory is controlled as a SRAM. All data is stored at fixed addresses in this memory, some of them I can only read and some I can read and write. This memory is 64KB in size.

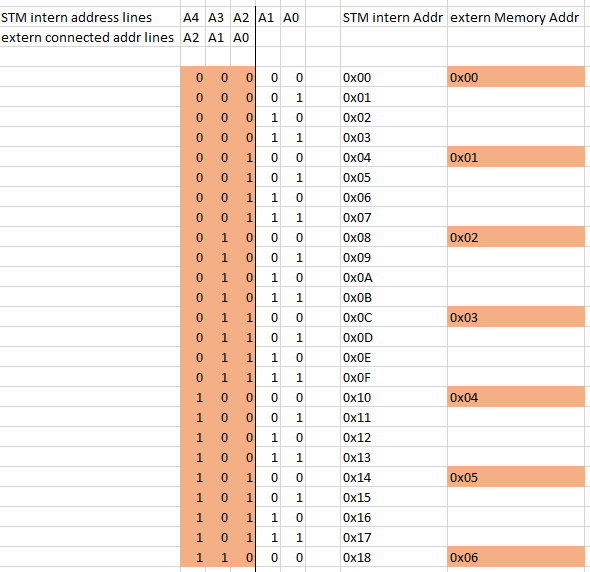

The problem is this extern memory is byte-addressed. So at every address there is one byte stored. So when I want to read the byte at address 0x04 at the external memory I have to set the internal address of STM to 0x10, because of the address shifting by two (see my table, the red one is the physical memory connection from A2-A0). I connected A0 to A0, A1 to A1 and so on. STM shifts the address by two and so intern address line A2 is then the address line A0 to my memory.

Its a bit confusing, I set my MPU region as none cachable from address 0x60000000 with the size of 64KB. But with the address shifting by two, do I have to set the memory size to 4*64 KB? To address the last byte in my memory (address 0x6000FFFF) I have to set the internal address in STM to 0x6003FFFC. This address is then shifted right by two.

So I have to calculate the external address before I can access any byte. As example I want to read the byte at address 0x06, so I calculate the internal address to 0x60000018.

Or is there an other more easy way?

Thank you for your answers.

Regards,

Dani

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-27 08:21 AM

The problem is this extern memory is byte-addressed.

What is that external memory? Post link to its datasheet.

Why do you insist on 32-bit bus, if you want 8-bit transfer?

JW

- Parallel ATA (IDE) to SD adapter diy in STM32 MCUs Embedded software

- STM32F407 I2C Addressing Problem in STM32 MCUs Products

- STM32F407 SDIO CLK line is running below 400 kHz in STM32 MCUs Products

- STM32F407 and recommendation for 3-Port Ethernet-Switch. in STM32 MCUs Embedded software

- Hardware IPv4 checksum on an STM32F407 is not working, though all the proper settings are set. (Works on rare occasions, oddly) in STM32 MCUs Embedded software