- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32F4, wish list for 2012.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F4, wish list for 2012.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-01-06 10:30 AM

1 - STM32F405RE / RC

2 - Analog comparator with DAC reference. 3 - Embedded ethernet phyter. 4 - PGA. #least-likely-prediction-for-2013- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-01-06 12:11 PM

I'll add to your list:

5. All RAM accessible via DMA 6. ''data count'' register on DCMI 7. Working hardware flow control on SDIO 8. I/O voltage control for SDIO Frank.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-01-09 11:30 PM

I'll add to your list:

9. DMA NDTR should be 32bit- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-01-10 1:41 AM

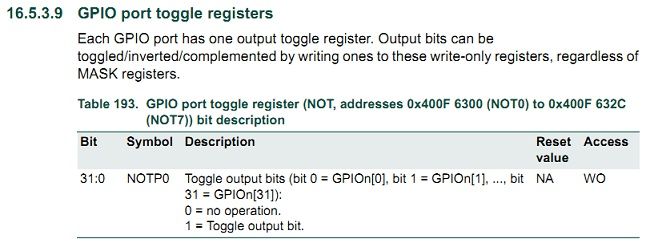

10. Atomic GPIO pin toggling by writing the BSRR register both set and reset bits to 1.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-01-10 12:10 PM

I think they won't do this (create toggle bit command), as this would get quite complicated for the processor to manage. This would be a Read-Modify-Make command, and together with these many bus structures, this gets very complicated - nearly impossible to implement this in a save atomic way.

Do you have an example, where you would really need such a toggle command very much, or is it just something ''nice to have'' for you?- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-01-10 8:49 PM

Some NXP parts have this feature which I find quite useful.

While we are at it, SDRAM support will be nice.

While we are at it, SDRAM support will be nice.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-01-11 2:53 AM

It wouldn't be the processor to manage it but the GPIO peripheral...

The only change is to give the S/R bits of the BSRR register the same truth table of a JK flip-flop, you don't need more registers or ''commands'', it fits in the current GPIO architecture. Use case? everywhere you need to change the state of a pin *without* having to do a read/modify/write or having to make it into a critical zone because you need atomicity. Nothing transcendental, already seen on other platforms and the only feature missing in the GPIO. Giovanni- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-01-11 6:00 AM

11. Decent documentation for the peripheral libraries.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-01-11 6:55 AM

12. SDIO clock support upto 50MHz for SD card

13. McBSP interface- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2012-01-11 9:17 AM

I'm not sure what's being wished for here as the F4 design is unlikely to change.

My STM32 gripes are 16-bit timers, all should be 32-bit, chained timers can't be accessed atomically. See also 32-bit counters, DMA, etc. Timer Wizard, need something to generate timer code or examples, for all possible use cases. DMA Wizard, something to illustrate possible connections, timers, peripherals, limitations, etc. Sure I can read the documentation, but some kind of ''fitter'' tools would be useful to allocate peripherals, pins and resources. SPI 8 or 16-bit, this is incredibly inflexible, need programmable bit length, more flexible rate generation. Stupid integer divider/prescalers, get some NCO/DDS using adders not incrementers. At low frequencies the jitter isn't an issue, and gives incredible range of possible frequency settings.Up vote any posts that you find helpful, it shows what's working..

- HAL GPIO assert fails for GPIO_AF3_TIM10 on STM32F4 devices in STM32 MCUs Embedded software

- STM32CubeController doesn't recognize STM32f3348-discovery in STM32CubeProgrammer (MCUs)

- install micropython onto stm32f407 discovery using Stm32CubeProgrammer in STM32CubeProgrammer (MCUs)

- Abnormal behaviour with STM32CubeMX in STM32CubeMX (MCUs)

- USB cdc, CDC_SET_LINE_CODING and CDC_GET_LINE_CODING in STM32 MCUs Embedded software