- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32f4 Discovery ADC problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32f4 Discovery ADC problem

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-20 03:52 AM

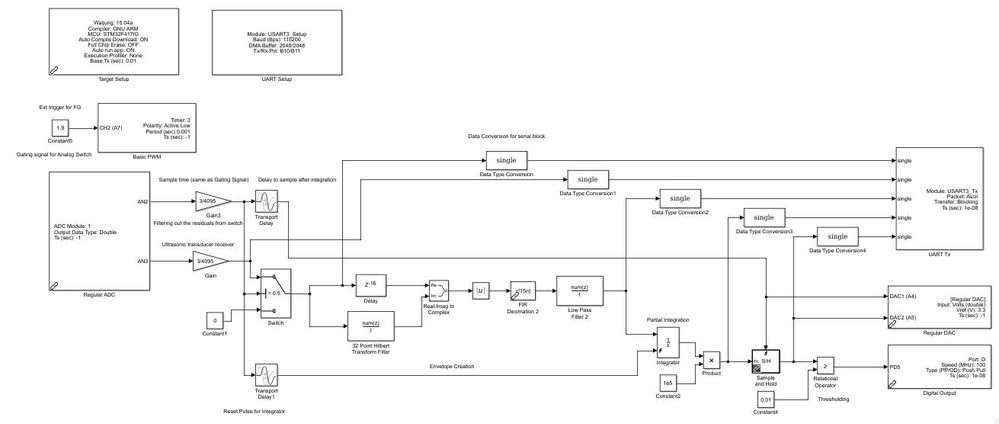

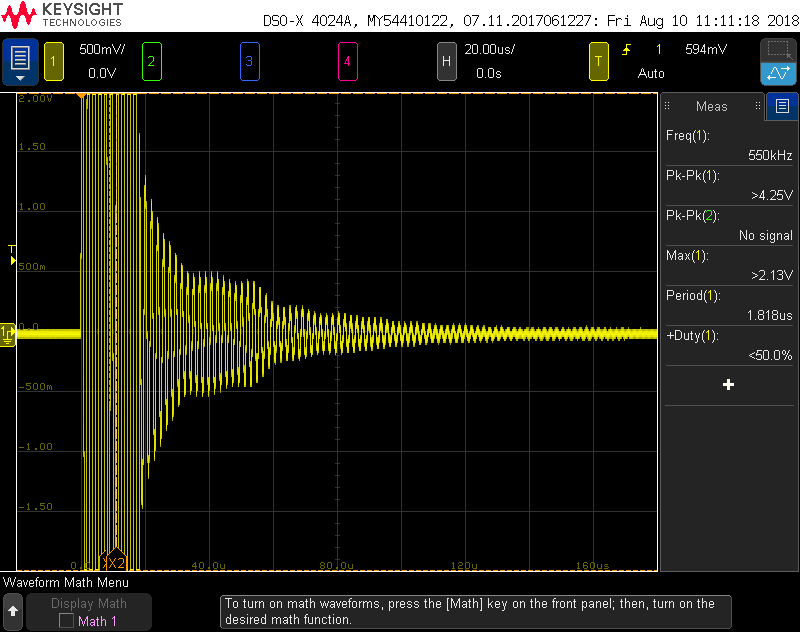

I am trying to do a partial integration on a 550 KHz waveform using STM32F4 Discovery board using the Waijung toolset in Simulink. The sampling time that I am using is 0.018 us, i.e 3 cycles if the clock frequency is 168 MHz. The ADC prescaler is 2, so the ADC frequency is 84 MHz. The total time required for the conversion should be 0.143 us (12 bit resolution) +0.018 us i.e. around 0.16 us. This should theoretically suffice the Nyquist criteria for sampling. However, I dont seem to get any output at the end. I can't see the real time data after ADC, using the serial interface or the DAC. So I am not sure what I am doing wrong. Any suggestions or ideas is much appreciated.

P.S. I am attaching the waveform I am trying to acquire (integration between say 20 us to 140us) and the simulink program. Please let me know if any other information is required.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-20 04:11 AM

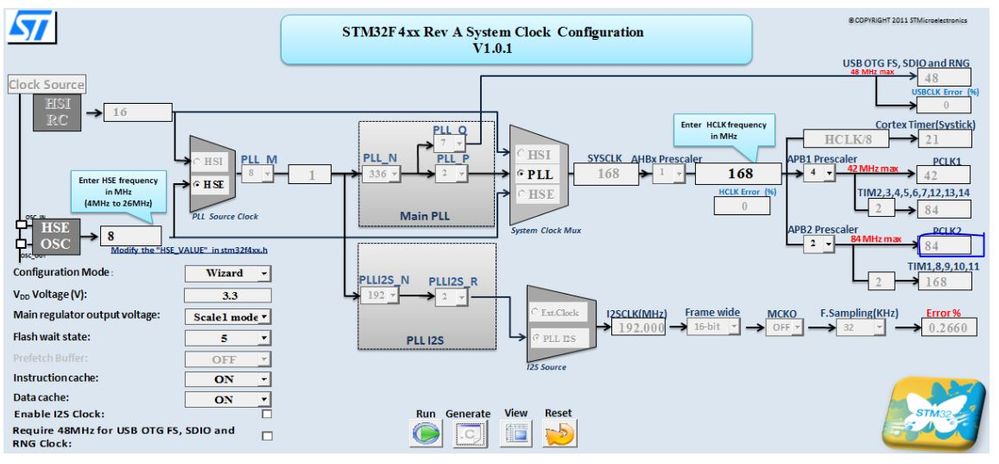

> The sampling time that I am using is 0.018 us, i.e 3 cycles if the clock frequency is 168 MHz.The ADC prescaler is 2, so the ADC frequency is 84 MHz

I don't think so. 84 MHz is far beyond the max. ADC clock, check the datasheet.

Not to mention, 12 MByte/sec is a bit beyond the UART capabilities, and the DAC has settling times of a few microseconds.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-20 06:09 AM

According to the clock config file, PCLK2 is 84 MHz by default. So if I consider another prescaler of 2 after this, the frequency would be 42 MHz (the datasheet says Fplck2/prescalar). I understood that the UART or the DAC wouldn't work, but I was trying whatever I could. My main motivation is to get the digital output that I am trying to obtain after the integration of the curve and the comparator. With the 42 MHz frequency this should be at least achievable, isn't it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-20 06:52 AM

Not sure if we speak about the same device.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-20 06:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-20 11:41 PM

I was referring to the Reference Manual, but I also found the one you are talking about. Seems like making the ADC work at that frequency will be a stretch. With a single ADC, there will only be around 3-4 samples per cycle at a data rate of 2 MSps. Although it still suffices the sampling criteria, do you think practically getting the data out contnuously at that rate is feasible? Sorry I haven't got much experience with this, so would gladly like to hear some views.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-21 02:04 AM

Well you could certainly sample at the limits of the ADC, but you'd need a deep enough buffer to decimate the interrupt loading, because you've really want that below 100 KHz, and perhaps much slower if you plan on doing a lot of math/processing on the data.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-21 02:51 AM

And getting out 3 samples at 2 Msps would mean about 12 MBps, meaning approx. 120.000.000 bps for the UART (assuming 10 bits per byte).

And as Clive mentioned, processing 3..4 values at that sample rate in real-time is ... at least a challenge.

Consider a real DSP with the ability to execute several instructions at once. These devices are made for a considerable instruction load in tight interrupt loops.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-24 12:40 AM

Thank you everybody for the insights.

- STM32H750B-DK Debug issue with SCB_EnableDCache in STM32 MCUs Products

- stm32f0 EXTI cubemx platformio in STM32CubeMX (MCUs)

- Suggestion to improve the usability of STM32CubeMX in the configuration of GPIOs in STM32CubeMX (MCUs)

- SSD1963 with STM32F407 using FSMC in STM32 MCUs Products

- Problem with a STM32F746G-DISCO Board and an Arduino shield in STM32 MCUs Boards and hardware tools