- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32CubeMX PLLSAI config for STM32L4

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32CubeMX PLLSAI config for STM32L4

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-11 12:31 PM

Thank you for your response.So far this solvesthe issue.

I will highjack this thread to ask additional questions.Ido not know if this is also connected with 1.9.0 or it is a known issue (samePLLSAI1 clk config, but with additional peripherals, on 1.6.0 works).I am using custom board with STM32L476 on it.

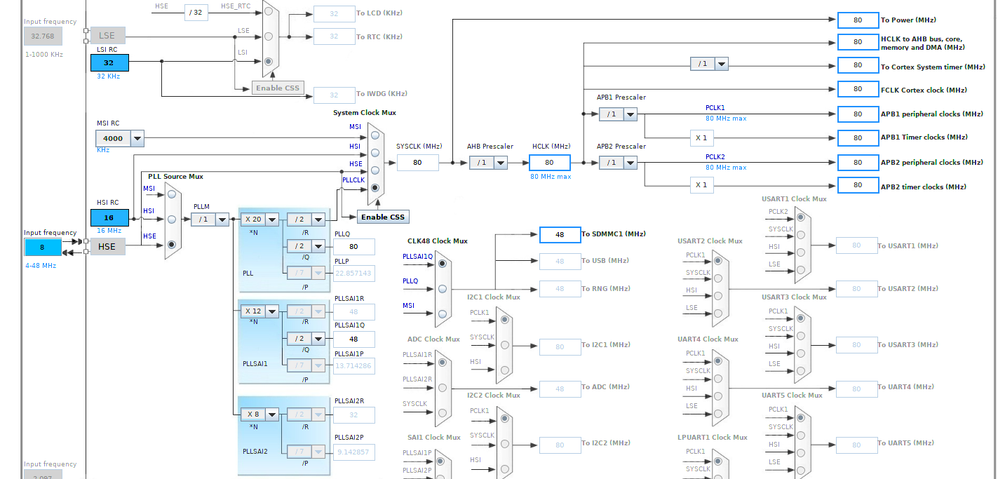

I use CubeMX to generate code, i only set SD, JTAG, and RCC peripherals Clock config as shown on provided image:

Generated project (without changing anything in it) successfully builds, but itfails in file

''stm32l4xx_hal_rcc_ex.c'' line 2948(using 1.9.0 package)

#if !defined(RCC_PLLSAI1M_DIV_1_16_SUPPORT)

||

(((READ_BIT(RCC->PLLCFGR, RCC_PLLCFGR_PLLM) >> RCC_PLLCFGR_PLLM_Pos) + 1U) != PllSai1->PLLSAI1M)

#endif�?�?�?�?(it eventually evaluatesto ''[7]+1 !=1'').

I admit i did not research this further, but it is the first time i generated project with CubeMX and peripheral timing asserts failed on such configuration. And a general question. What is the state of STM provided eMMC (with possible FatFs) peripheral code for L4 family of cards? Will it beprovided at anytime, or will it always generate placeholders in code?- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-23 5:32 AM

quick updates, if in future somebody gets to similar problem.

There is a missing line in system clock config*

PeriphClkInit.PLLSAI1.PLLSAI1M = 1;

Second issue was not setting 'SDMMCCLK divider factor' in 'Configuration->SDMMC1' window. I set it to 250 so i am under 200KHz (i didn'texperiment with other values), for beginning of communication with eMMC card. This seems tobe OK for my configuration. Adapt as need for your PLL config. I will try higher freqs when my eMMC driver will be stable.That sadly also means myquestion about stable eMMC driver for L4 is still valid

:)

* i recall i found the issue already reported somewhere on this forum, but i can not find the thread again...Something with new CubeMX version not including this line...

Edit: Found the thread:

- STM32CubeMX with MMT: strange LD file generation in STM32CubeMX (MCUs)

- Debug Authentication stuck at "SDM Library version v1.3.0" in CLOSED state in STM32 MCUs Security

- The list of #include in the main.c file is lost when regerating stm32cubemx with new GPIO config. in STM32CubeMX (MCUs)

- Object initialization silently skipped with picolibc due to missing linker symbols in STM32CubeIDE for Visual Studio Code (MCUs)

- CubeMx error in STM32CubeMX (MCUs)