- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32 I2C SCL SDA DELAY PROBLEM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32 I2C SCL SDA DELAY PROBLEM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-26 7:31 PM

Hi, I am currently using two SMT32F207 for I2C transmission (MASTER writes SLAVE). Below is my configuration and waveform diagram.

The problem currently encountered is that once the bit changes from 1 to 0 (HIGH to LOW)

The transmission of SCL and SDA will be delayed for a period of time, but this will not happen when it goes from 0 to 1. I would like to ask seniors how to solve this problem?

The way I connect is to connect the SCL, SDA and GND of the two pieces to each other. (PB8 is connected to PB8, PB9 is connected to PB9), both blocks use I2C1 configuration, then MASTER uses interrupt transmission, and SLAVE uses interrupt reception.

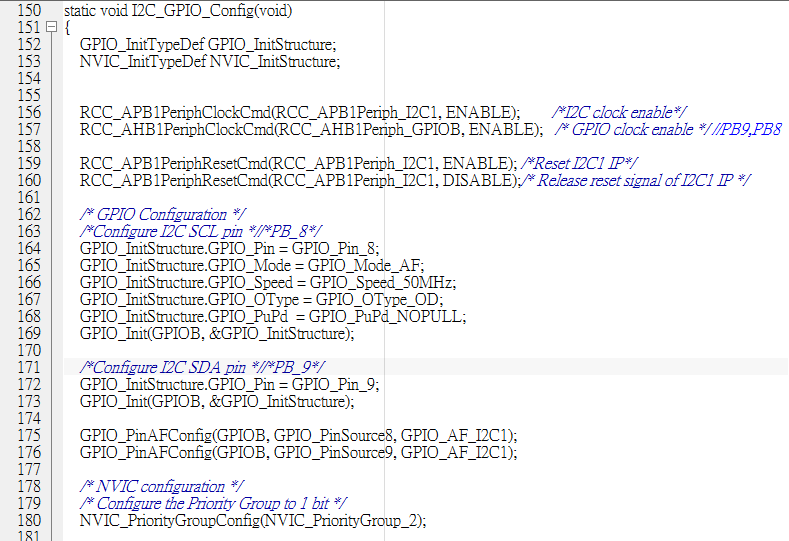

GPIO:

SCL:PB8

SDA:PB9

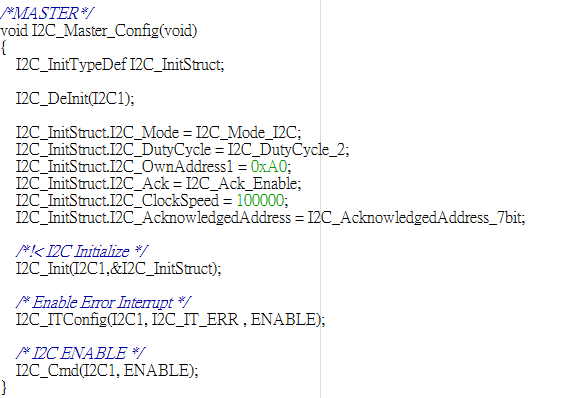

MASTER_I2C_CONF:

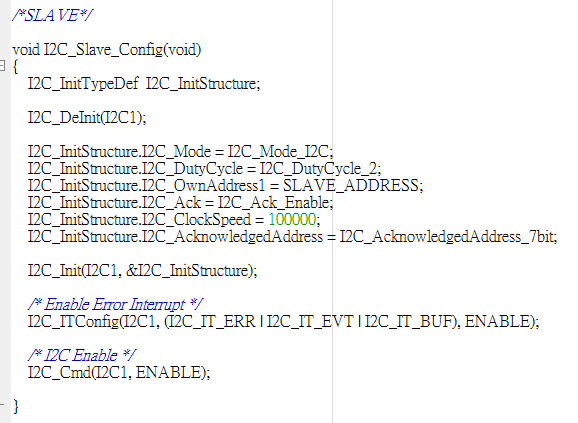

SLAVE_I2C_CONF:

Wave_Graph:

This situation has both ADDRESS and DATA.

Please help me answer this question, and thank you to everyone who responded.

- Labels:

-

I2C

-

Interrupt

-

STM32F2 Series

- STM32WB09KEV6TR custom PCB: STLINK-V3PWR SWD fails with "Unable to get core ID" in Others: STM32 MCUs related

- PWM input output drift in STM32 MCUs Products

- STM32G431 Bootloader issue in STM32 MCUs Products

- Debug STLink GDB Server v.1.3.0 - PARSE ERROR: Argument: -cp in STM32CubeIDE for Visual Studio Code (MCUs)

- Double buffer flicker / inequality in STM32 MCUs TouchGFX and GUI