- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- SPI slave interrupt is slow in STM32F767

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SPI slave interrupt is slow in STM32F767

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-02-19 10:58 PM

I am working on SPI slave at NUCLEO-F767ZI.

I am using the interrupt and LL library. This is the RX handler:

void SPI1_Rx_Callback(void) {

if (LL_SPI_GetRxFIFOLevel(SPI1) > LL_SPI_RX_FIFO_HALF_FULL)

{

// this is only for break point

spi1_rx = LL_SPI_ReceiveData16(SPI1);

return;

}

spi1_rx = LL_SPI_ReceiveData16(SPI1);

spi1_tx = spi1_rx;

LL_SPI_TransmitData16(SPI1, spi1_tx);

}It just echos. The master sends 70 bytes data with no delay or gap until the end of the transmission. I put a break point in the line of 5 in the above code. When the master sends the data in 1MHz, it never go into the break point. But if I increase it to 2MHz, it stops in the break point. I think 2MHz is not that fast speed in SPI bus. How can I fix this?

- sysclk: 96MHz

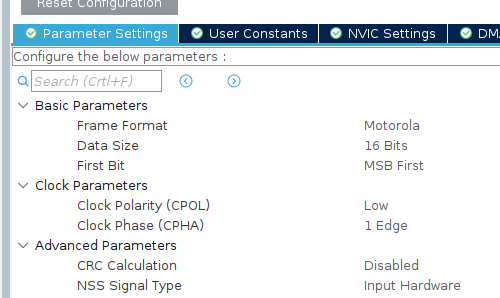

- Here is SPI1 setting:

Solved! Go to Solution.

- Labels:

-

SPI

-

STM32F7 series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-02-20 2:19 AM

Hello @YoungKim

DMA can help to get faster data transfer rates. You can configure the DMA controller to transfer data between the SPI peripheral and a memory buffer.

Also, you may use DMA interrupts to trigger a callback function when a transfer is complete and set up the DMA to transfer data at a fixed number of bytes, which can be set to the maximum length of data that the master will send in each burst.

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

Best regards,

FBL

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-02-19 11:54 PM

Its easy to get interrupt latencies >1µs especially if you work with the HAL callback mechanism and not the bare IRQ handlers. A typical approach could read from RX FIFO in a while loop to drain the FIFO as quickly as possible. Another approach would be using DMA which seems preferrable here because the master sends short bursts (of predictable max. length?) of data.

hth

KnarfB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-02-20 2:19 AM

Hello @YoungKim

DMA can help to get faster data transfer rates. You can configure the DMA controller to transfer data between the SPI peripheral and a memory buffer.

Also, you may use DMA interrupts to trigger a callback function when a transfer is complete and set up the DMA to transfer data at a fixed number of bytes, which can be set to the maximum length of data that the master will send in each burst.

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

Best regards,

FBL

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-02-20 2:45 PM

The SPI slave application should respond as soon as possible whenever it receives 16 bits register. therefore the DMA solution may not be suitable. Is my understanding correct?

And I can't use while loop solution because I am running multiple tasks by using FreeRTOS.

I want to use bare IRQ handler. I will try and get back here with the result. Thanks @KnarfB and @F.Belaid

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-02-20 2:50 PM

If the chosen STM32 has it, use DMA TX and RX channels in cyclic buffer mode.

This way, you mostly need to deal with NSS going up EXTI detection to digest the data transfer.

Some SPI with 32 bit HW FIFO aren't fully application optimized, thei TX FIFO being full by DMA in slave mode, when NSS goes up, and the only way to flush the FIFO is to RCC/SYS reset/reconfigure the SPI. These workarounds are necessary to get something decently working in the real world instead of the cycle count optimisation world.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-02-21 2:45 PM

I found this from the RM0410 reference manual:

It is preferable for the slave to use DMA, especially when data frames are shorter and

bus rate is high.

- SPI Comminication between two microcontrollers in STM32 MCUs Embedded software

- L0 I2C slave RX DMA - clean cancel with I2C STOP ? in STM32 MCUs Products

- SPI_WaitOnFlagUntilTimeout() hangs after few cycles of SPI_DMATransmitReceiveCplt() in STM32 MCUs Embedded software

- STM32F401 as I2C Slave Mode? Speed? in STM32 MCUs Products

- G474 SPI DMA sync occasionally missed? in STM32 MCUs Products