- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- SPI Master NSS always low in STM32F4

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SPI Master NSS always low in STM32F4

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-03 3:34 AM

Hi guys!

I'm configuring the Nucleo 64 with the STM32F446RE to use SPI as a Master.

The problem I'm having right now is that the NSS pin is always low. Clock and MOSI are perfect. What I would like is that the NSS is high, and goes low during the transmission, then high again.

I've tried setting the NSS as Hardware output, and Software in Cube, but still failed to get what I want.

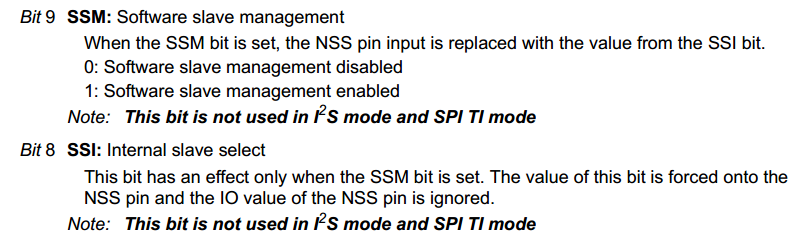

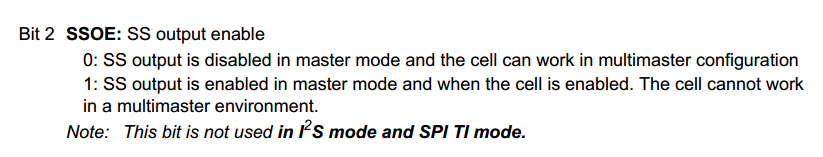

I think this configuration should be sorted with the following 3 bits, from CR1 and CR2. Right now Cube is setting SSOE= 1, SSM=1, SSI=1. And the NSS pin is configured as hardware output in Cube.

Any clues on how should I setup this? I would like to avoid having to use a random pin as CS and pull it manually.

Thanks!!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-03 7:52 AM

Hey Nemui. Tried it but I still get nothing.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-03 2:28 PM

But most of the SPI slaves need the CS edge to trigger (capture) the internal shift register to memory.. so you need to trigger the CS even though you might be sending 100 bytes.

I know. The designer of the STM32 SPI module did not know. Why are you so surprised? Chipmakers employ mere people, no superheroes. It annoys me too, and then what. Move along, nothing to see here.

But I'm still curious, because even though SPE=0, NSS stays low.

I don't have an 'F4 at hand now but I guess it goes Hi-Z. Try to swich on a pullup on it.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-03 3:16 PM

>>I know. The designer of the STM32 SPI module did not know. Why are you so surprised? Chipmakers employ mere people, no superheroes. It annoys me too, and then what. Move along, nothing to see here.

Sometimes I think they employ interns with no practical experience programming peripheral hardware, and see minimal gate count as a priority over functional usefulness. Some places employ geniuses who can actually design and test complex logic, and have it work first time around, worked with some in the 80's and 90's, with a lot better cross-discipline understanding of where optimum balance of functionality vs gate count was located. I'm sure ST has some of them too, one of the MEMS guys is awesome, but they were probably weren't on the initial STM32 team when some of the design choices were baked in.

I like the STM32 a lot, but there is a bunch of brain damaged design in some of the peripherals and clocking, I live with it.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-03 6:05 PM

Just to add a little context, once you've committed an idea to silicon it is very disruptive to change that in subsequent releases/revisions. The STM32 families have been kept very consistent, and you don't have to check steppings to deal with dozens of anomalies.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-15 7:56 PM

Hi,

I had to face the same problem, but on the STM32F105, SPI master + DMA and hardware NSS.

Before I had found the issue it looked like this

After reading the discussion I realized that disabling the SPI in DMA callback resolves the issue.

static void SpiCallback(SPI_HandleTypeDef *hspi)

{ __HAL_SPI_DISABLE(hspi); // disable NSS };void HAL_SPI_ErrorCallback(SPI_HandleTypeDef *hspi)

{ SpiCallback(hspi); };void HAL_SPI_TxRxCpltCallback(SPI_HandleTypeDef *hspi)

{ SpiCallback(hspi); };void HAL_SPI_TxCpltCallback(SPI_HandleTypeDef *hspi)

{ SpiCallback(hspi); };After that transmission looks like this.

I hope it will help you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-10 8:13 AM

Pullup worked, thanks! I wish the documentation had indicated HiZ...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-10 8:23 AM

Hello to all!

It is not writen in any RM or DS that NSS pin in Master mode, is responsible to control the CS of a slave device and to provide the necessary timing for this!

It is very clear also, in Master mode, that NSS pin is kept low when master enabled until the master is disabled.

So this is not a problem. is the normal behaviour of SPI Master NSS pin.

When a Master keep the NSS pin low in a multi device bus , this means that all devices (with same NSS functionality) will be forced to act as slaves and will not try to act as Masters.(if properly configured for this ofcourse).

When the Master frees the NSS line, informs the bus that any other device can take the control of the bus as a new Master by forcing his NSS pin low.

Conclusion. If you want to have one Master on the bus , and only slave devices , inside Master's device the NSS functionality is useless and the GPIO can be used as an ordinary pin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-12 6:00 AM

Hello. I had the same problem with stm32l0. When you use hardware NSS (on master).

1. SPI_CR2_SSOE = 1

2. Hal lib always enable SPI on transfer. So you should disable SPI when finish transfer (__HAL_SPI_DISABLE)

3. Set pullup for NSS gpio pin in GPIO_PUPD

This setup work for me.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-11-07 3:16 PM

THis tripped me up for a while too. Even when the STM32F is set to be the bus master, with HW NSS, the STM32F drives it low, but doesn't drive it high when not selected! Thus if you start out looking at the NSS pin, it looks like nothing's happening.

Unless there is some configuration I missed, the pin must be independently pulled up, either externally, or via the internal GPIO pull-up. (Which is too weak to allow rapid consecutive SPI transactions.)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-11-07 10:46 PM

> Even when the STM32F is set to be the bus master, with HW NSS, the STM32F drives it low,

> but doesn't drive it high when not selected!

By "not selected", you mean that you set SPI_CR1.SPE=0? Try toggling that bit, i.e. clear it, then immediately set it again.

JW

- STM32F103 Input PWM capture signal with different width in STM32 MCUs Products

- I2C slave on a STM32F030T4P6 with HAL callbacks not working in STM32 MCUs Products

- Stm32 stopped working after soldering components in STM32 MCUs Products

- I2C detect repeated start condition in STM32 MCUs Embedded software

- OCTOSPI as simple QUAD/Dual/Single parallel-to-serial output on STM32H5xx in STM32 MCUs Products