- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Sensible Configuration for Timer Triggered Con...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Sensible Configuration for Timer Triggered Continuous STM32F4 ADC Sampling

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-15 07:35 AM

Hi all,

I am about the configure the timer frequency which will trigger ADC to continuously scan and convert 5 channels. The callback will be from DMA.

The MCU I am using is STM32F407. System core clock is 168 Mhz. Fpclk1 = 42MHz, Fpclk2 = 84MHz...

A question came up when setting the ADC clock prescaler, and the overall configuration between the timer frequency and ADC settings. What would be the max or logical value?

My idea is as follow, please help to comment or correct me if I am wrong, without considering the external impedance.

I wanted to trigger the ADC every 84 kHz from a selected timer.

There are 5 channels to scan and convert in a row, 12 bit resolution and 15 sampling cycles for each channel.

Understanding from datasheet that typical fadc is 30 MHz, so does this mean that a sensible set of configuration would be limited by the following parameters:

- Fadc prescaler should be >=4 ?

- Timer frequency should be <= ( Fadc / ( channel_cnt * ( sample_cycle + conversion_cycle ) )?

Thank you.

#timer-triggered-adc #stm32f407- Labels:

-

STM32F4 Series

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-15 07:41 AM

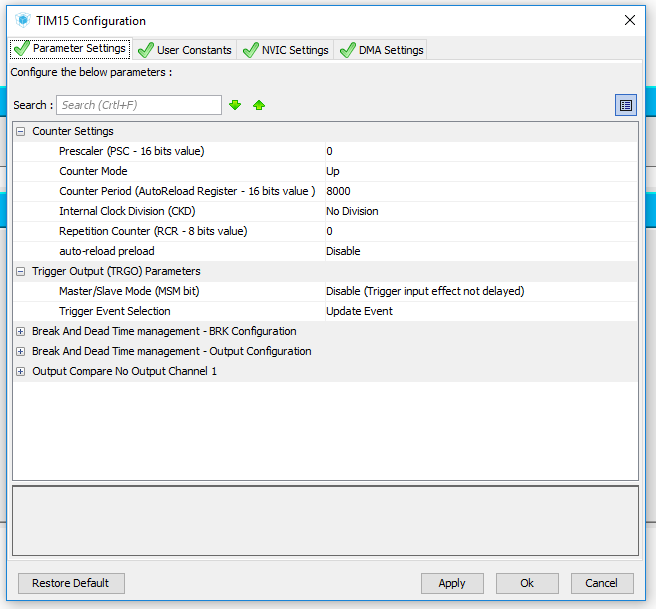

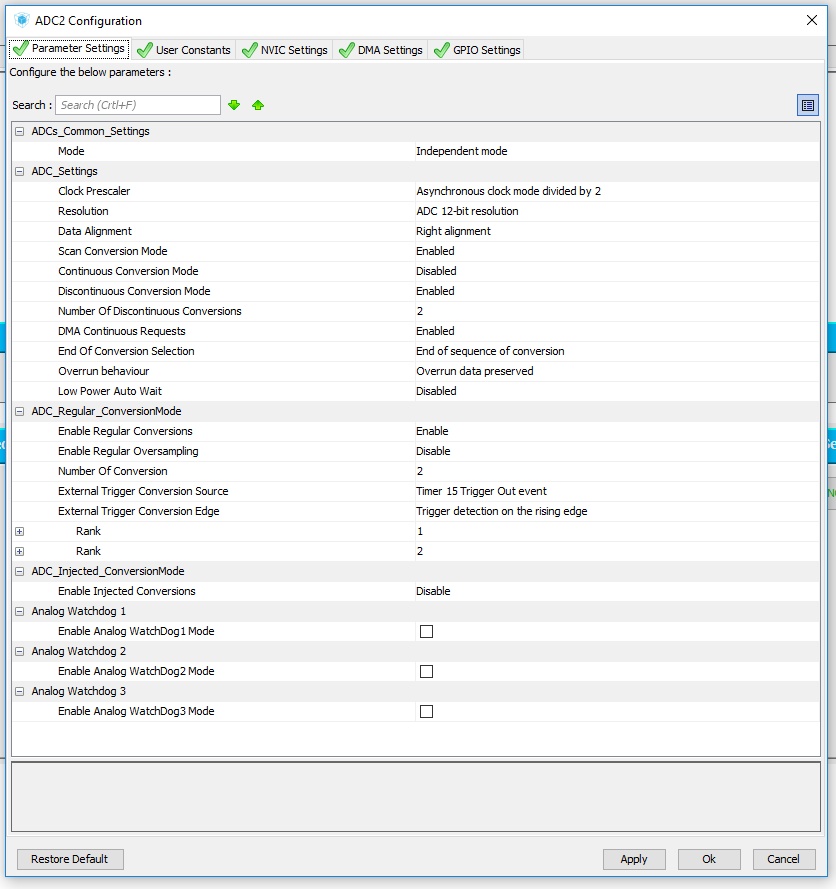

Something like this...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-15 07:43 AM

The more sensible solution is to use a TIM to pace the ADC, one can play games with the prescaler/sample time on the ADC side but fitting that manually is tedious, and a bit inflexible. The TIM's prescaler/period are integer which does provide for some headaches, but can usually be addressed by tuning the SYSCLK.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-15 08:51 AM

Hi Clive One,

I am getting a little more confused now. Please forgive my ignorance. My question arose when I am trying to use a TIM TRGO to pace the ADC sampling. So, TIM TRGO is set and ADC External Trigger Source and Enable bit are set accordingly..

If my understanding is right, that trigger pulse will only kick start the scanning and conversion, and the real process is still clocked by the ADC clock..

So my question point to a set of sensible setting which will not cause overlapping TIM triggering and not overclocking the ADC, while getting the max performance out of the two.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-15 09:14 AM

This is what my example does. I am using TIM15 to create a trigger for the ADC using the Update Event. This then causes the ADC to sequentially reads 2 channels and uses DMA to put the results in memory. After a number of the DMA sequences have happened I process the data.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-15 11:08 AM

Hi Andy,

I know how to do this with Timer and ADC peripherals, my real question was the sensible TIM frequency and ADC prescaler values...

- ADC: stuck inside HAL_ADC_GetValue() in STM32 MCUs Embedded software

- EVSPIN32G4NH - opamp ADC (OPO1) doesn't work in STM32 MCUs Motor control

- STM32H753ZI UART DMA issue in STM32 MCUs Embedded software

- Implementing STM32L4S5ZIT6 Bootloader with a Memory Marker in STM32 MCUs Products

- stm32wle5ccu6 stopmode disables programming in STM32 MCUs Products