- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- retriggerable one pulse mode in CubeMX

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

retriggerable one pulse mode in CubeMX

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-11 8:47 AM

Hey everyone,

Got a little issue that I'm a little confused on.

I want to use a one pulse mode to output a pulse of length dependent on the input signal.

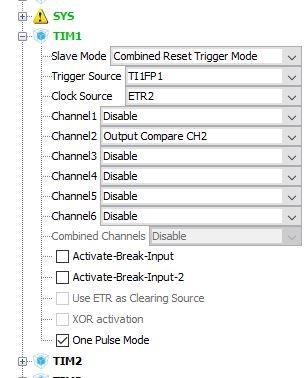

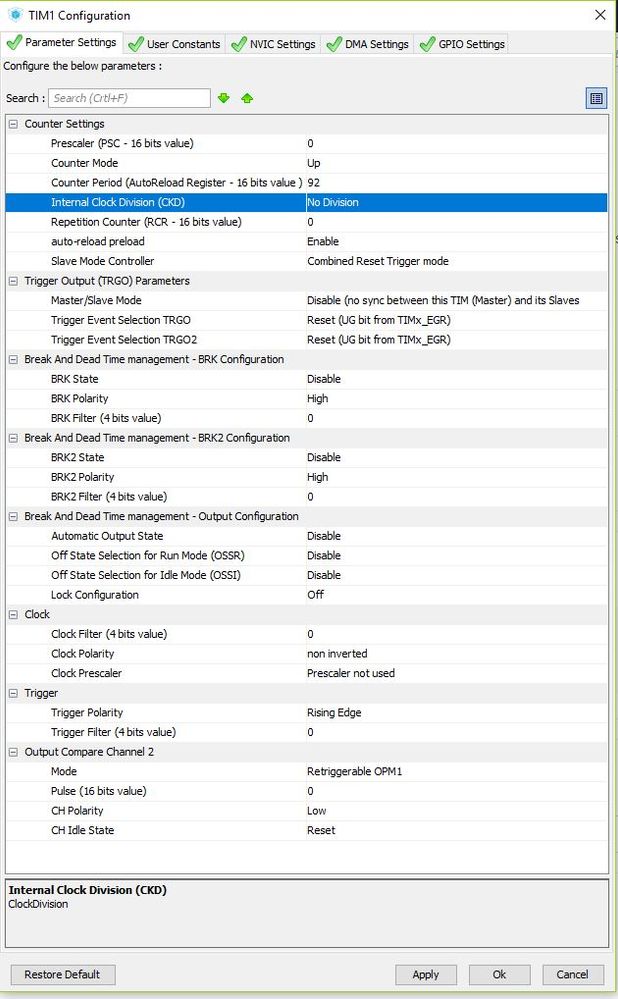

So essentially, when the trigger goes off, I want the pulse length to be 92 clock cycles long of the ETR2 clock. These clock cycles will be fed in from the external clock input.

So I've added ETR2 as my clock input, this will increment the counter. The trigger to tell the device to output the pulse is connected to TI1FP1 and the output of the pulse will be on capture compare CH2. I've also enabled one pulse mode on the tick box.

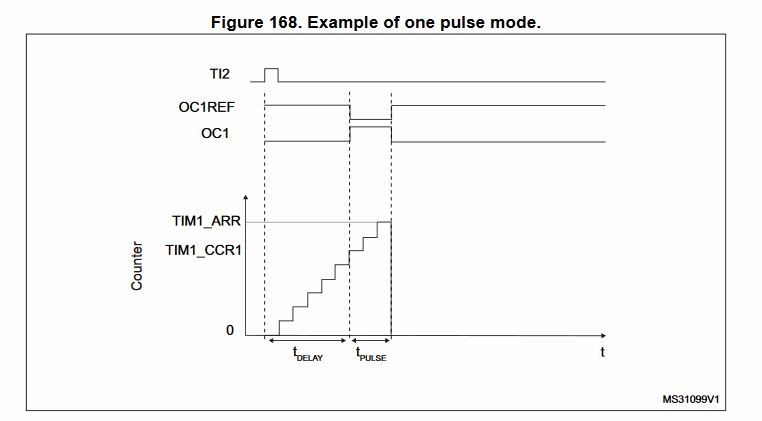

In the configuration its set to Retriggerale OPM1. My understanding is that once the trigger has been done, the pulse will be outputted after the delay, and will last until the an overflow occurs from the ARR.

Further than that I have a question:

The pulse length will be dependent on ETR2's clock input although the timer will still be internally clocked at its bus frequency. I essentially want this Delay to be as small as possible.So I'd need to set the OCxFE bit, After this bit is set It seems the delay will be around 3 clock cycles, will this be clock cycles of the internal clock or the external? My understanding is internal but just want to triple check.

Thanks in advance for any help!

stm32f7- Labels:

-

STM32F7 Series

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-08-10 9:30 AM

Sorry, bumping old zombie unanswered threads off my feed

Up vote any posts that you find helpful, it shows what's working..

- Timer options for DMA transfer on STM32F03F4P6 in STM32 MCUs Products

- [STM32H743VITx] PWM Configuration in STM32 MCUs Products

- Timer 1 Retriggerable One-Pulse Mode in STM32 MCUs Products

- STM32F407 Waveform with TIM and DMA in STM32 MCUs Products

- STM32G474 Dual Simultaneous ADC question in STM32 MCUs Embedded software